应用于射频的集成无源器件硅基转接板技术

摘要

展示了一种应用于射频微系统领域的可以集成射频无源器件的硅基转接板结构。该结构将电感、电容、电阻、传输线和 TSV 等集成在适用于微波应用的高阻硅衬底上,可实现芯片级的CMOS 、 MMIC 及 MEMS 多种不同材料器件集成。采用这种方法制备的传输线损耗在 40 GHz 为0.34 dB/mm ,电容密度达到 1.05 fF/μm 2 , 2.5 圈 8 nH 电感最大 Q 值在 1.5 GHz 达到 16 。这项制造技术与 CMOS 制造工艺兼容,可为超高集成度的三维集成型化射频微系统提供有力支撑。

引言

过去几十年中,电子器件一直遵循摩尔定律通过减小加工线宽提高器件性能。近年来随着加工精度下降,到达 9 nm 甚至更小以后摩尔定律开始难以为继。半导体行业发展的重点逐渐转移到小型化、多功能的微系统上,即所谓的超越摩尔路线。同时,随着 4G 通信的广泛应用,5G 通信的产业化布局,应用于移动通信领域的低成本高集成度的射频模块需求呈现爆发式增长。集成无源器件(IPD)和硅通孔(TSV)技术是实现微系统小型化的关键。相比于低温共烧陶瓷(LTCC)等传统的厚、薄膜工艺,硅基 IPD 成本更低,体积更小,微波性能也更胜一筹。更重要的是,硅基 IPD 技术可以通过标准的CMOS 半导体制造工艺与微波 MMIC 芯片集成 ,充分利用硅基半导体加工精度高集成度高的特点实现大规模量产。在同时集成 IPD 和 TSV 的晶元上还可以进行圆片级三维堆叠和无引线键合。但在传统 CMOS 工艺体系上同时集成 IPD 与 TSV 是一项复杂的工作,特别是针对微波应用,需要同时在材料、工艺和架构上进行创新 。比如,标准 CMOS工艺采用的低阻硅衬底和薄铜布线结构会给高频IPD 器件带来很大损耗。TSV 的集成方式和对系统微波性能的影响也需要进行评估。

本文介绍了一种基于标准 CMOS 工艺,同时集成 IPD 与 TSV 的微波应用方案。采用无定形硅(SIPOS)被用来简化硅衬底表面钝化,并采用 2 μm的厚铜工艺用于减少微波损耗提高器件 Q 值。

1 转接板整体架构和制造方法

本文介绍的是在传统硅基 CMOS 工艺基础上,针对微波射频应用,开发出的可用于射频微系统集成的硅基转接板技术。该技术将传统大马士革薄层铜工艺加厚,用于减小微波损耗;将射频TSV 引入硅片用于微波信号的垂直传输;将整个圆片减薄至 100 μm 用于进一步减小堆叠体积。整套工艺架构简明,扩展性强,可作为三维射频微系统的标准化模块使用。

1.1 硅基转接板架构

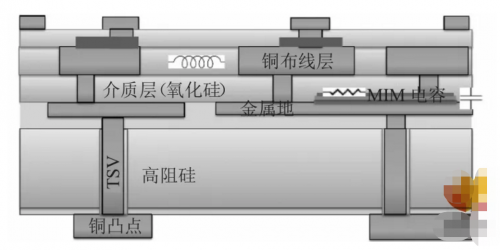

同时集成 IPD 和 TSV 的硅基转接板架构如图 1 所示,该结构主要包含 4 个部分,自下而上依次为:用于信号垂直传输的 TSV 结构;底层金属布线;金属 - 介质 - 金属(MIM)结构;两层金属间的高密度微互联通孔结构;上层金属布线以及用于信号传输的金属触点。厚铜结构在微波应用中可以减小 IPD 的损耗提高器件 Q 值。在下图结构中,上层铜布线的厚度达到 2 μm 。衬底采用大于10 kΩ·cm 的高电阻率硅晶元,用以防止微波信号耦合进衬底。同时,硅片表面用一层 SIPOS 钝化层来降低表面电荷密度。转接板表面可以制备高密度金属微凸点阵列,通过低温共晶键合的方式将CMOS、MMIC、MEMS 等不同材料不同功能的器件集成上去。这种架构的优点是可以以一个转接板为基础,继续向上堆叠延伸,进而实现微系统完整功能。

图 1 集成 IPD 和 TSV 的硅基转接板架构图

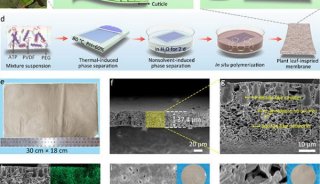

1.2 硅基转接板制造方法

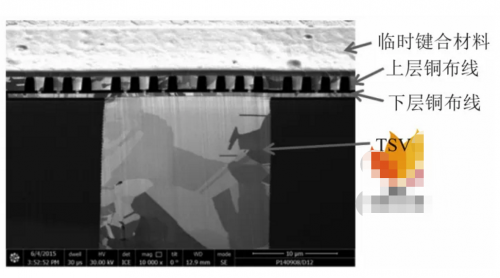

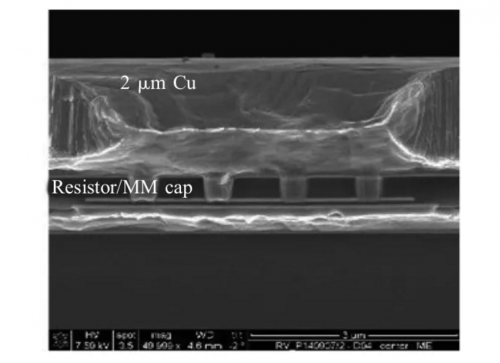

同时集成 IPD 和 TSV 硅基转接板制造流程为:采用一块 200 mm(8 英寸)电阻率 10 kΩ·cm的单抛硅片,通过高深宽比 ICP 刻蚀、阻挡层 / 种子层沉积和铜电镀等一系列工艺实现孔径 20 μm、深度 85 μm 的 TSV 结构;对晶元正面抛光后,采用大马士革铜工艺电镀上 600 μm 的金属层,底层金属主要作为接地层、MIM 电容的下层金属以及多圈电感结构的底部连接;紧接着制备 MIM 电容,电容采用 50 μm TaN/60 μm SiN/50 μm TaN 的三明治结构。上层 TaN 可同时作为电阻层;再往上是一系列 500 nm 直径、500 nm 深的高密度铜互联通孔阵列,用于底层金属及 MIM 电容与上层金属的互联;上层金属是 2 μm 厚铜结构,用于传输线和多圈电感结构;最后采用临时键合工艺将圆片翻转减薄至 85 μm 的 TSV 露出。在本文中我们采用铝材料做凸点用于性能测试,实际使用中也可以制成高密度铜凸点用于键合互联。图2 是硅基转接板的截面电镜扫描图,图 3 是金属层、铜互联阵列及 MIM电容层的放大图,展示出高精度的硅基加工工艺。

图 2 硅基转接板的截面电镜扫描图片

图 3 上下层铜金属及 MIM 层的放大图

2 硅基转接板性能测试

电感、电容及传输线等结构均采用上述工艺实现。本文所有数据均采用均匀分布在 200 mm(8 英寸)晶元上的 16 个器件测试,用于评估工艺技术的良率及一致性。测试方式均为通过底部TSV 触点测试,信号由底部触点通过 TSV,经无源器件,再由 TSV 导出。单个 TSV 损耗经测试在 10 GHz 为 0.1 dB。

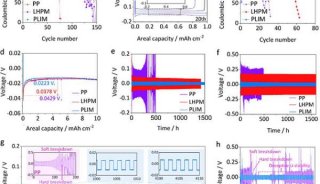

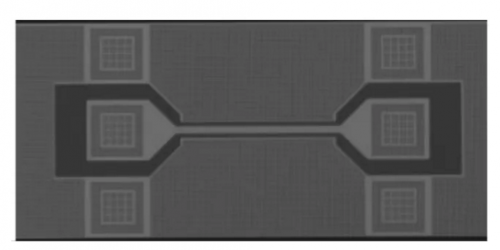

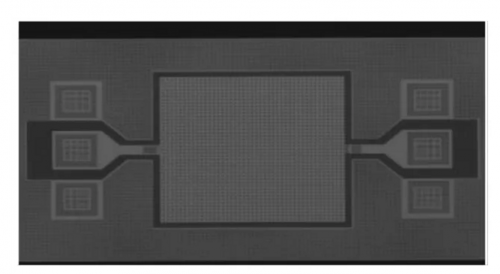

CPW 传输线位于 2 μm 厚的上层铜布线层,如图 4 所示。结构采用 GSG 形式,正面触电通过TSV 引至背面。

图 4 传输线结构俯视图

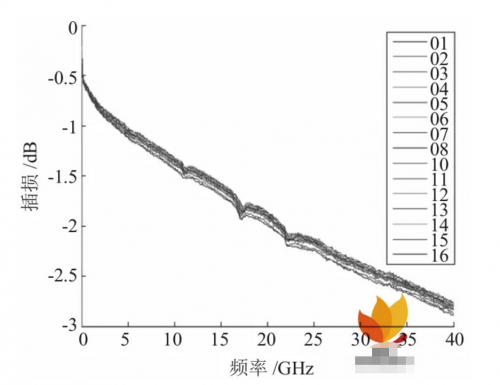

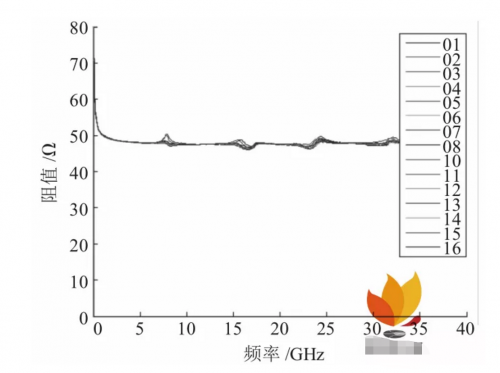

图 5 和图 6 分别是 8 mm 长、20 μm 宽的传输线损耗和阻值,传输线损耗在 40 GHz 频率下约为 0.34 dB/m,阻抗均为 50 Ω。

图 5 传输线损耗测量值

图 6 传输线阻抗值

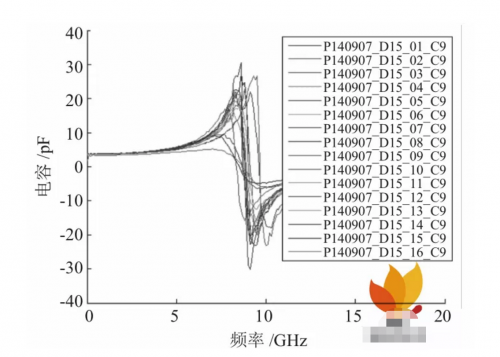

MIM电容如图7所示,该电容面积为3 600 μm 2 。图 8 是测量结果,平均电容密度达到 1.05 fF/μm 2 ,满足工程应用需求。

图 7 MIM 电容结构俯视图

图 8 MIM 电容容值测量结果

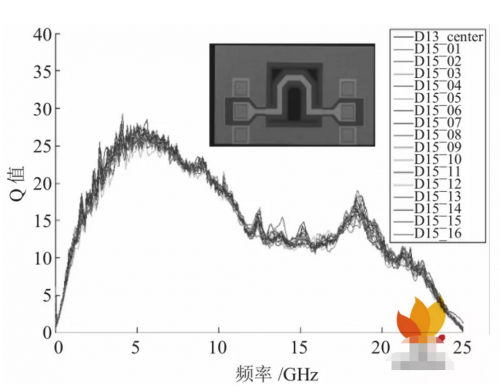

图 9 所示是半圈电感的 Q 值数据,电感线圈直径 60 μm,线宽 25 μm。16 个电感测试数据一致,表现出良好的片内均匀性。最大 Q 值在 5 GHz为 27,电感感值为 4 nH。

图 9 半圈电感 Q 值测量结果

多圈电感采用不同金属层间的绕圈及空气桥结构,图 10 所示电感是一个 2.5 圈,内径 150 μm,线宽 30 μm 的结构。最大 Q 值在 1.5 GHz 时达到16,对应感值 8 nH。后续可以通过增加介质层厚度的方法继续提高 Q 值。

图 10 2.5 圈电感 Q 值测量结果

3 结束语

针对未来多功能一体化射频微系统的需求,本文提出了一种集成 IPD 与 TSV 的硅基衬底转接板方案。高性能的电阻、电容、电感等无缘集成器件在该技术架构下得以实现。我们针对微波应用需求,在传统 CMOS 工艺基础上开发了厚铜金属化工艺和硅表面 SIPOS 钝化工艺用以减小损耗提高性能。本文提出的架构可以实现微波 / 直流信号的垂直传输,硅基转接板可以进一步进行三维堆叠集成,为未来微波组件 / 系统芯片化提供了一条标准化工艺途径。(参考文献略,作者黄旼 ,朱健等)