CRC循环冗余校验的原理与算法及FPGA实现(三)

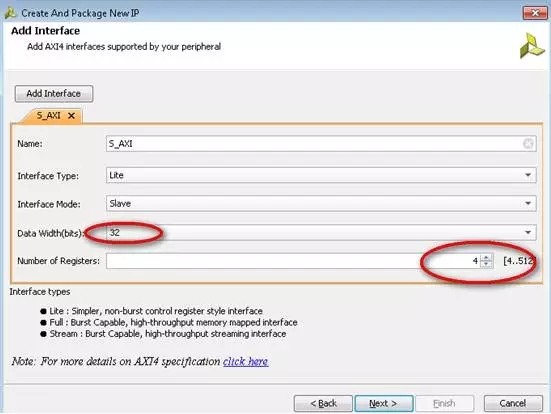

6)更改AXI总线名字,添加4个32位的slv_reg寄存器,其实都是默认的即可

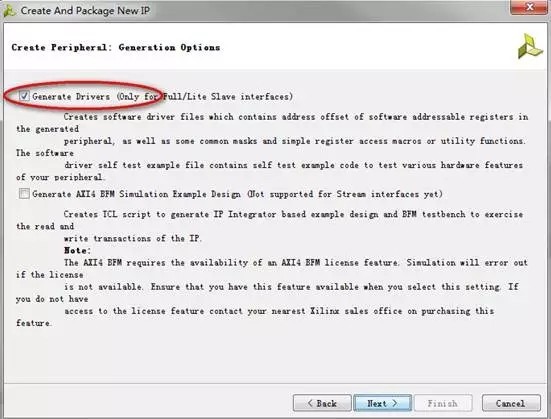

7)选择Generate Drivers,点击next,然后finish

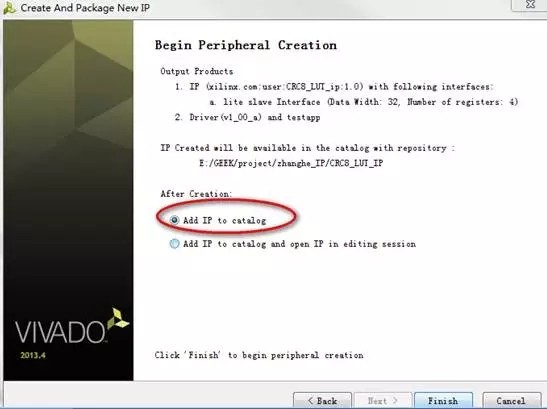

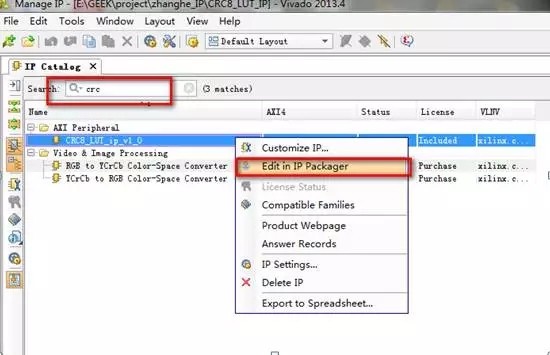

8)这样我们就可以在IP Catalog下搜索CRC,就会找到自己生成的IP核“CRC8_LUT_ip_V1_0”, 然后右键选择Edit in IP Packager,这样就会打开IP核编辑界面:

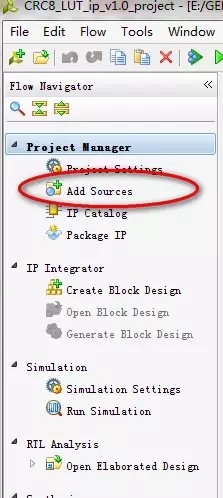

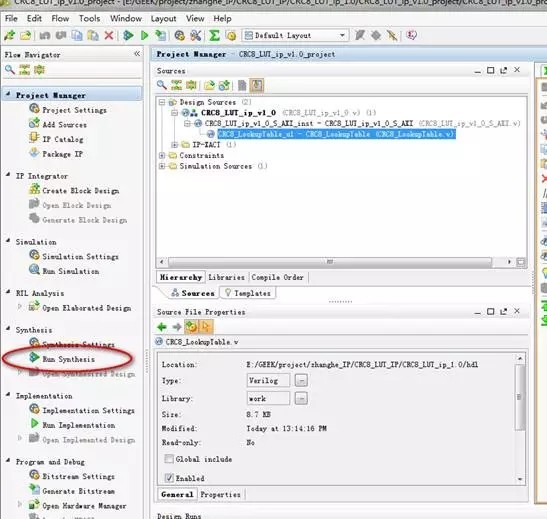

9)在flow navigator栏中选择 add aoirce 添加之前自己编辑的CRC算法的.v文件,即CRC8_LookupTable.v

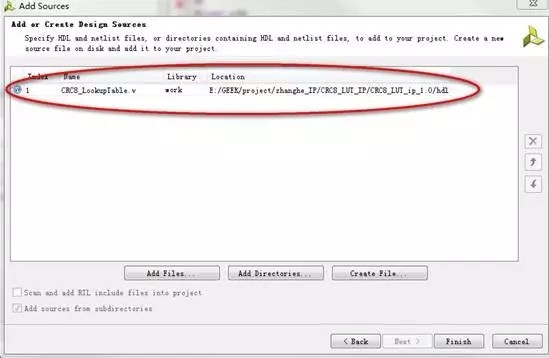

10)会发现在工程里一共3个.v文件:

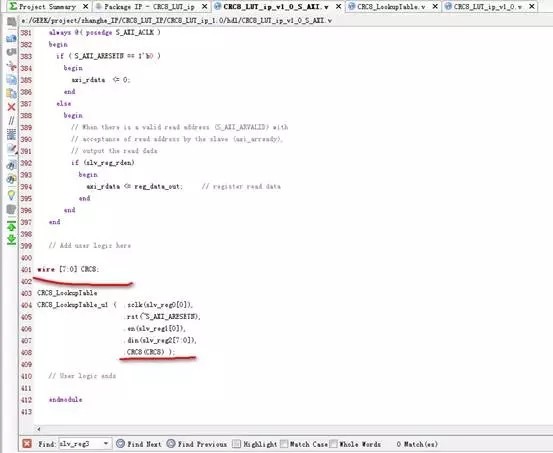

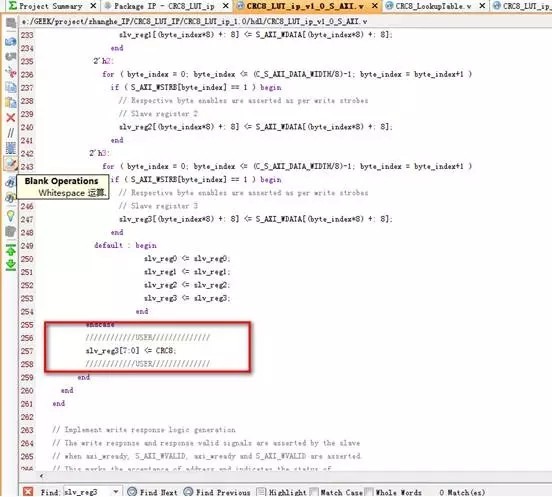

CRC8_LUT_ip_v1_0_S_AXI.v 和 CRC8_LUT_ip_v1_0.v 和刚刚添加的自己的CRC8_LookupTable.v文件,然后需要修改CRC8_LUT_ip_v1_0_s_AXI.v 文件,把我们的IP核挂载到AXI总线上,其实就是一个简单的例化过程。由于我所创建的IP核不需要和FPGA外部通信,不用分配引脚,只需和AXI总线通信,所以就不用在CRC8_LUT_ip_v1_0_S_AXI.v添加用户input或者output,只需把slv_reg 0 1 2 3 分别连接到sclk、en、din和CRC8.

由于slv_reg3是一个寄存器型的,所以要定义一个wie型变量CRC8,再连接到slv_reg3,不然综合会出错。

11)然后保存,综合,如果报错,继续修改综合,知道没有报错。

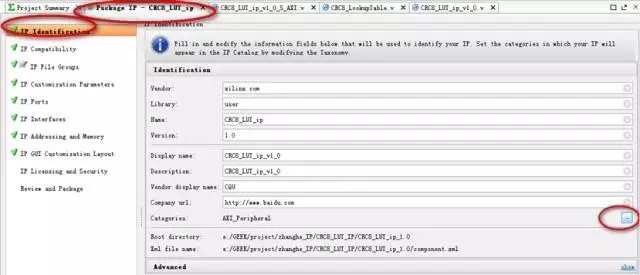

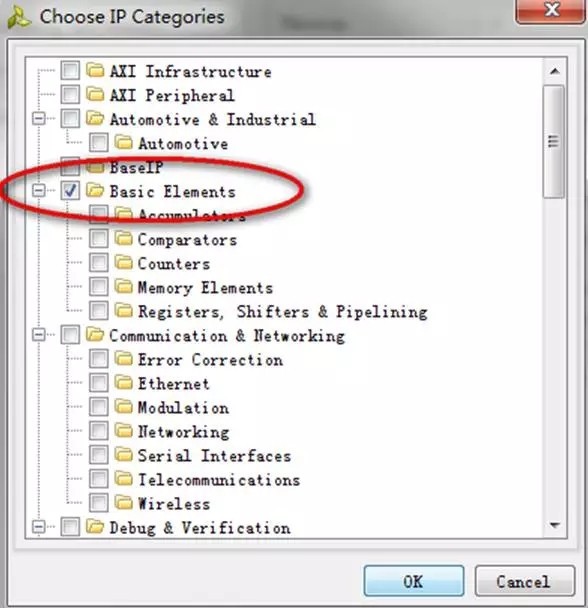

12)综合完成后,点击Package IP-CRC8_LUT_ip标签页,点击Categories ,选择我们的IP核将会出现在IP catalog的哪个类别里面,如果选择“basic elements” 就会在IP catalog的basic elements类别下找到,如图

13)添加IP核支持的芯片型号,也就是添加family,因为要在microZed板子上跑,所以要把zynq系列添加进来

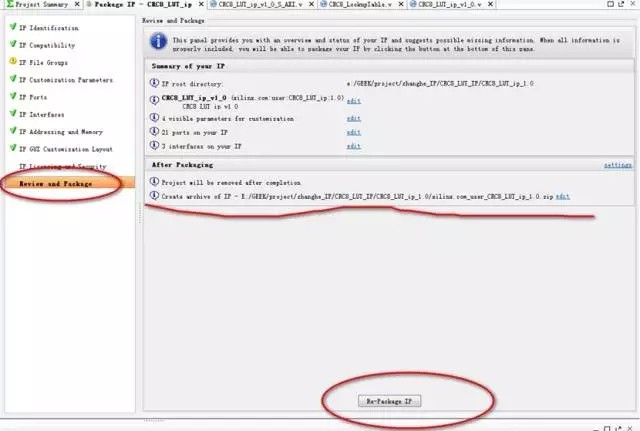

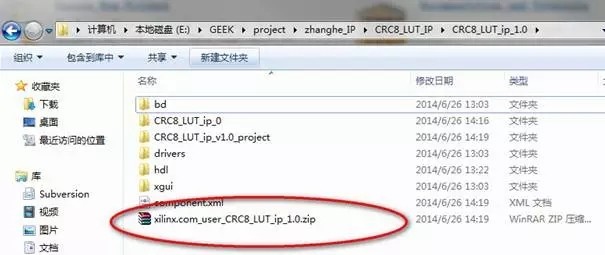

14)最后封装IP,如果我们能在Create archive of IP所示的路径下找到这个压缩文件,就说明我们的IP制定成功了~