5G毫米波无线电射频技术演进 (二)

近期最实用、最有效的波束合成方法是混合数模波束成型,它实质上是将数字预编码和模拟波束合成结合起来,在一个空间(空间复用)中同时产生多个波束。通过将功率引导至具有窄波束的目标用户,基站可以重用相同的频谱,同时在给定的时隙中为多个用户服务。虽然文献中报道的混合波束成型有几种 不同的方法,但这里显示的子阵方法是最实际的实现方法,本质上是模拟波束成型的步骤和重复。目前,报告的系统实际上支持 2 到 8 个数字流,可以用于同时支持单个用户,或者向较少数量的用户提供 2 层或更多层的 MIMO。

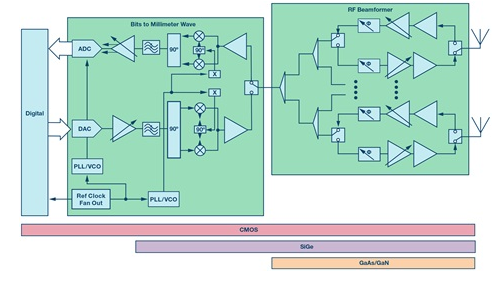

让我们更深入地探讨模拟波束成型的技术选择,即构建混合波束成型的构建模块,如图 3 所示。在这里,我们将模拟波束合成系统分为三个模块进行处理:数字、位到毫米波和波束成型。这并非实际系统的划分方式,因为人们会把所有毫米波组件放在邻近位置以减少损耗,但是这种划分的原因很快就会变得很明显。

图 3. 模拟波束合成系统方框图

波束成型功能受到许多因素的推动,包括分段形状和距离、功率电平、路径损耗、热限制等,是毫米波系统的区段,随着行业的学习和成熟,需要一定的灵活性。即便如此,仍将继续需要各种传输功率电平,以解决从小型蜂窝到宏的不同部署情形。另一 方面,用于基站的位到毫米波无线电需要的灵活性则 要小得多,并且在很大程度上可以从当前 Release 15 规格中派生出来。3 换言之,设计人员可以结合多个波束成型配置重用相同的无线电。这与当前的蜂窝无线电系统没有什么不同,在这些系统中,小信号段跨平台很常见,而且每个用例的前端更多都是定制的。

当我们从数字转向天线时,就已经为信号链绘制了潜在技术的进展图。当然,数字信号和混合信号都是在细线体 CMOS 工艺中产生的。根据基站的要求,整个信号链可以用 CMOS 开发,或者更有可能的是,采用多种技术的混合开发,为信号链提供最佳性能。例如,一种常见的配置是使用具有高性能 SiGe BiCMOS IF 到毫米波转换的 CMOS 数据转换器。如图所示,波束成型可采用多种技术实现,具体取决于系统需求,我们将在下面讨论。根据所选的天线尺寸和发射功率要求,可以实现高度集成的硅方法,也可以是硅波束成型与离散 PA 和 LNA 的组合。

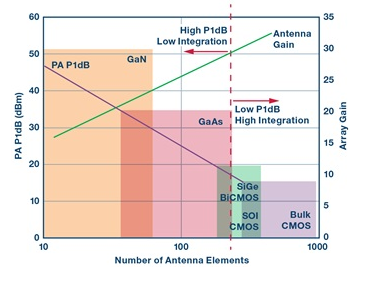

在之前的工作中,对变送器功率与技术选择之间的关系进行了分析,4,5 在此不再全面重复。但是,为了总结这一分析,我们在图 4 中包含了一个图表。功率放大器技术的选择基于综合考虑所需的变送器功率、天线增益(元件数)和所选技术的 RF 发电能力。如图所示,可以在前端使用 II-V 技术(低集成方法)或使用基于硅的高集成方法,通过较少的天线元件来实现所需的 EIRP。每种方法都有各自的优缺点,而实际的实现取决于工程在规模、重量、直流功耗和成本方面的权衡。为了为表 1 中导出的案例生成 60 dBm 的 EIRP,演示文稿“5G 毫米波无线电的架构与技术”5 中进行的分析得出,最佳天线尺寸介于 128 至 256 个元件之间,较低的数量通过 GaAs 功率放大器实现,而较大的数量可采用全硅波束成型基于 RF IC 的技术实现。

图 4. 60 dBm EIRP 的天线所需的变送器功率、天线尺寸和半导体技术选择之间的关系 5

现在让我们从不同的角度来研究这个问题。60 dBm EIRP 是 FWA 常用的 EIRP 目标,但数值可能更高或更低,具体取决于基站和周围环境的期望范围。由于部署情形变化很大,无论是树木成荫的地区、街道峡谷地区,还是广阔的空地,都有大量的路径损耗需要根据具体情况进行处理。例如,在假定为 LOS 的密集城市部署中,EIRP 目标可能低至 50 dBm。

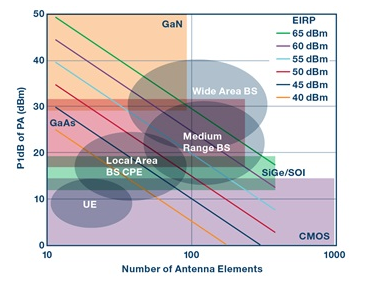

FCC 按设备类别 3,6 设定有定义和发布的规格,以及发射功率限制,这里我们遵循基站的 3GPP 术语。3 如图 5 所示,设备类别或 多或少地限定了功率放大器的技术选择。虽然这不是一门精确的科学,但我们可以看到,移动用户设备(手机)非常适合 CMOS 技术,相对较低的天线数量可以达到所需的变送器功率。这种类型的无线电将需要高度集成和省电才能满足便携式设备的需求。本地基站(小型蜂窝)和消费者终端设备(可移动电源)要求类似,涉及从变送器功率要求低端的 CMOS 到更高端的 SiGe BiCMOS 的一系列技术。中程基站非常适合 SiGe BiCMOS 技术,可实现紧凑的外形尺寸。在高端,对于广域基站来说,可以应用各种技术,具体取决于对天线尺寸和技术成本的权衡。尽管可在 60 dBm EIRP 范围内应用 SiGe BiCMOS,但 GaAs 或 GaN 功率放大器更适合更高的功率。

图 5. 基于变送器功率的各种毫米波无线电尺寸适配技术 5

T 图 5 显示了当前技术的快照,但行业正在取得很大进展,技术也在不断改进。如“5G 毫米波无线电的架构与技术”演示文稿中所述,5 提高毫米波功率放大器的直流功率效率是设计人员面临的主要挑战之一。

随着新技术和 PA 架构的出现,上面的曲线将发生变化,并将为高功率基站提供集成度更高的结构。演示文稿 ““近期高效毫米波 5G 线性功率放大器设计简短调查”7 中很好地概述了 PA 技术的进展。

我们再复习一下上面的观点,对波束成型部分进行总结。目前还没有一种万能的方法,可能需要设计各种前端设计来解决从小型蜂窝到宏的各种用例。

毫米波无线电:从位到毫米波及从毫米波到位

现在让我们更详细地讨论位到毫米波无线电,并探讨系统这一部分的挑战。关键是要将位转换为毫米波,再以高保真度转换回来,以支持 64 QAM 等高阶调制技术,以及未来系统中可能高达 256 QAM 的技术。这些新无线电的主要挑战之一是带宽。5G 毫米波无线电名义上必须处理 1 GHz 或可能更高的带宽,具体取决于频谱的实际分配方式。虽然 28 GHz 下的 1 GHz 带宽相对较低(3.5%),但假设是 3 GHz 中频下的 1 GHz 带宽,那么设计起来就更具有挑战性,并且需要某种先进技术来实现高性能设计。

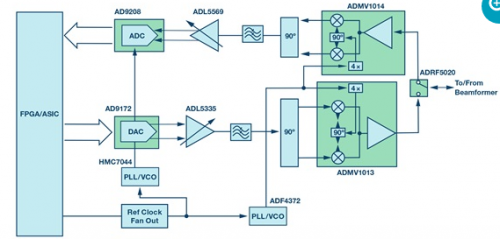

图 6 展示了一个基于组件的高性能位到毫米波无线电的方框图示例,构成 ADI 公司的宽 RF 和混合信号产品系列。该信号链经证实在 28 GHz 上支持连续的 8× 100 MHz NR 载波,具有出色的误差矢量幅度(EVM)性能。有关此信号链及其演示性能的更多详细信息,可参见 ADI 公司的 5G 毫米波基站视频。8

图 6. 宽带位到毫米波无线电框图

让我们来讨论一下数据转换器。在图 6 的示例中,我们显示了所 使用的直接高中频变送器发射和高中频接收器采样,其中数据 转换器在中频进行发射和接收。在能够合理实现的情况下,中 频要尽可能高,以避免在 RF 下的图像滤波困难,从而将中频驱 动到 3 GHz 及以上。幸运的是,先进的数据转换器能够在这种频 率下工作。 AD9172 是一款高性能、双通道、16 位 DAC,支持高达 12.6 GSPS 的采样速率。该器件具有 8 通道、15 Gbps JESD204B 数据输入端口、高性能片内 DAC 时钟倍频器和数字信号处理功能, 支持带宽和高达 6 GHz 的多频段直接至 RF 信号生成。在接收器中,我们显示了双通道、14 位、3 GSPS ADC AD9208。 该器件内置片内缓冲器和采样保持电路,专门针对低功耗、小尺寸和易用 性而设计。该产品设计支持通信应用,能够实现高达 5 GHz 的宽带宽模拟信号直接采样。

在发射和接收中频阶段,我们建议将数字增益放大器从单一转换为平衡,反之亦然,以避免使用巴伦。这里,我们在发射链中显示 ADL5335 在接收链中显示 ADL5569 作为高性能宽带放大器的示例。

对于中频和毫米波之间的上变频和下变频,我们最近推出了一种 基于硅的宽带上变频器 ADMV1013 和下变频器 ADMV1014。这些宽带变频器件的操作范围为 24.5 GHz 至 43.5 GHz。此频率覆盖范围广泛,因此设计人员用一种无线电设计即可处理目前定义的所有 5G 毫米波频段(3GPP 频段 n257、n258、n260 和 n261)。两种器件 均支持高达 6 GHz 的中频接口和两种变频模式。如图 6 所示,这两种器件都包括片内 4×本振(LO)倍频器,且 LO 输入范围为 5.4 GHz 至 11.75 GHz。ADMV1013 既支持从基带 I/Q 直接转换为 RF,也支持从中频进行单边带上变频。它在 24 dBm 的高输出 IP3 提供 14 dB 的转换增益。如果在单边带变频中实现,如图 6 所示,该器件提供 25 dB 边带抑制。ADMV1014 既支持从基带 I/Q 直接转换为 RF,也支持镜像抑 制下变频至中频。该器件提供 20 dB 的转换增益、3.5 dB 的噪声指数和–4 dBm 的输入 IP3。镜像抑制模式中的边带抑制为 28 dB。

RF 链中的最后一个组件是 ADRF5020 宽带硅 SPDT 开关。ADRF5020 在 30 GHz 时提供 2 dB 的低插入损耗和 60 dB 的高隔离度。

最后,我们来讨论频率源。考虑到本振可能占据 EVM 预算的很大一部分,因此使用一个相位噪声极低的来源来生成毫米波本振(LO)至关重要。

ADF4372 是一种具有行业领先集成 PLL 和超低相位噪声 VCO 的宽带微波频率合成器,输出功率可达 62.5 MHz 至 16 GHz。结合外部环路滤波器和外部基准频率使用时,可实现小数 N 分频或整数 N 分频锁相环(PLL)频率合成器。8 GHz 的 VCO 相位噪声在 100 kHz 偏移时为–111 dBc/Hz,在 1 MHz 偏移时为–134 dBc/Hz。

图 6 中的方框图对于任何考虑 28 GHz 和 39 GHz 频段毫米波设计的设计人员来说都是一个很好的起点,适合与需要高性能宽带无线电的各种波束合成前端配合使用。ADI 的 射频、微波和毫米波 产品选型指南 中也列出了许多组件,其他信号链架构或类似高频应用的设计人员可能会对这些组件感兴趣。

总结

最近几年,毫米波无线电发展迅猛,离开实验室发展到了现场试验,并将在接下来的几个月进行商业部署。不断发展的生态系统和新出现的用例要求波束合成前端具有一定的灵活性,但正如讨论的那样,有一些适合近天线设计的技术和方法可供选择。无线电的宽带特性(位到毫米波)需要前沿技术,但基于 硅的技术正在迅速发展,以满足混合信号和小信号域的要求。基于目前可用的组件给出了一个高性能无线电设计示例。

随着 5G 生态系统的不断发展,ADI 公司将继续利用我们的领先技术和信号链解决方案,支持客户为新兴的 5G 毫米波市场开发差异化系统。

参考电路

1 Thomas Cameron。 ““微波行业的 5G 机遇与挑战。” Microwave Journal, 2016 年 2 月。

2 Theodore S. Rappaport, Yunchou Xing, George R. MacCarthy, Jr., Andreas F. Molisch, Evangelos Melios 和 Jianhua Zhang。 “第五代(5G)无线网络毫米波通信概述——以传播模型为重点。” IEEE Transactions on Antennas 和 Propagation, 5G 特刊, 2017 年 11 月。

3 3GPP 38.104 技术规范。 基站(BS)无线电发射和接收(Release 15)。

4 Thomas Cameron。 “5G 毫米波无线电 RF 技术。”ADI 公司,2016 年 11 月。

5 Thomas Cameron。 “5G 毫米波无线电的架构与技术。”2018 国际固态电路会议,Session 4,面向 5G 和未来的毫米波无线电,2018 年 2 月。

6 简报:为新一代(5G)无线宽带识别和开辟大量新高频频谱的频谱前沿方案。

7 Donald C. Lie, Jill Mayeda 和 Jota Lopez。 “近期高效毫米波 5G 线性功率放大器设计简短调查。” 2017 年 IEEE 第 60 届国际中西部电路和系统研讨会(MWSCAS),马萨诸塞州波士顿,2017 年 8 月。

8 5G 毫米波基站。ADI 公司。