Science:IBM科学家造出世界上最小的晶体管

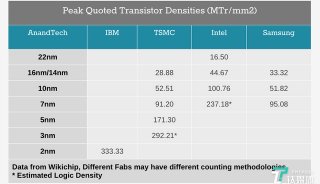

巨头英特尔(Intel)创始人之一Gordon Moore在1965年提出了业界著名的“摩尔定律(Moore's Law)”,大意为:集成电路上的元器件(例如晶体管)数目,每隔18个月至两年便会增加一倍,性能也将提升一倍。摩尔定律在一定程度上反映了现代电子工业的飞速发展,但时至今日,随着硅基晶体管的材料和制造工艺逐渐接近理论极限,这种“飞一般”的速度终于慢了下来。

科学家们想进一步缩小晶体管的尺寸,以在单位面积的芯片上集成更多晶体管,这样芯片会变得性能更强而价格更低。碳纳米管是目前替代硅材料的热门之选,一些有关的工作也时常见诸报道,比如加州大学伯克利分校Ali Javey教授的栅极长度仅有1纳米的晶体管(Science, 2016, 354, 99,点击阅读详细),以及北京大学彭练矛-张志勇课题组的5纳米碳纳米管CMOS器件,将晶体管性能推至理论极限(Science, 2017, 355, 271, 点击阅读详细)。

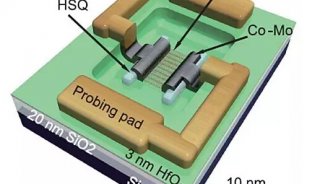

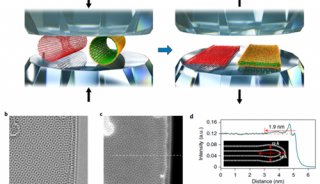

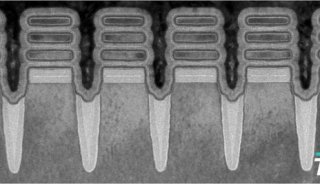

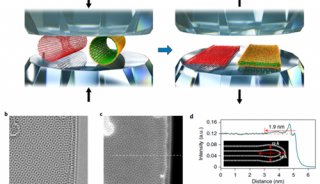

不过,如果当前基于碳纳米管的晶体管要实现最佳性能,它的尺寸甚至还要比硅基晶体管大,而现在最先进的所谓“14 nm制程工艺”硅基晶体管的实际尺寸(footprint)在90 nm左右。原因之一在于,这些基于碳纳米管的晶体管为了降低接触电阻,不得不使用长度在100 nm至200 nm的源极和漏极触点。近日,IBM研究中心的曹庆(Qing Cao)等人在Science 发表文章,使用了一种新策略来制造碳纳米管晶体管的触点,在减小尺寸同时保持了较低的接触电阻。为了保证在触点间传输足够的电流,他们在触点之间设置了由数根平行半导体碳纳米管(s-CNT)组成的阵列。最终制得的p-沟道晶体管,尺寸仅有40 nm,是目前报道的最小记录。不仅如此,更值得称道的是,电学测试表明这种新型s-CNT晶体管比现在的硅基晶体管更快更高效。

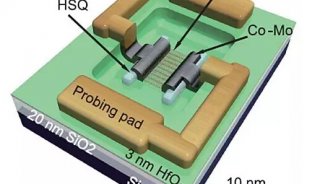

新型s-CNT晶体管结构示意图。

本文第一作者和通讯作者曹庆是本领域的知名青年科学家,2016年他还曾因在碳纳米管基晶体管方向的相关贡献,入选了MIT Technology Review 评选的“年度35岁以下创新35人”(35 Innovators Under 35,MIT TR35)[1]。

工作中的曹庆

科学家已经知道,在晶体管中使用钼触点直接连接s-CNT的开放端部,可以将触点长度缩短至10 nm左右,同时还能保持较低的接触电阻。不过,问题在于相关工艺要求在850 ℃下的高温退火,这对制备60 nm以下的沟道来说是灾难性的,就算使用钼,结构稳定性也很难保证。本文作者的解决方案是添加钴,使得钼-钴合金与s-CNT的直接连接在较低温度(650 ℃)下也能实现,在缩短触点长度的同时保持较低的接触电阻。温度的降低,使得触点在成型的同时,漏极-源极电极即使间隔小于20 nm也能保持结构稳定性。

另外,作者采用多根平行s-CNT构成阵列的方式来提高触点间的传输电流,而且这种基于s-CNT阵列的晶体管总尺寸依然限制在40 nm。而在随后的电性能测试中,这种s-CNT晶体管比目前的硅基晶体管速度更快、效率更高。

曹庆表示,这种新型碳纳米管晶体管所面对的主要挑战是器件稳定性。为了在集成电路中集成数十亿个这种晶体管,需要保证晶体管具有良好的一致性,这样才能在相同电压下,所有晶体管都能正常工作。

-

焦点事件

-

科技前沿

-

焦点事件

-

焦点事件