漫谈半导体工艺节点(二)

可能的选择

短期内,芯片制造商们明确地会在FinFet和二维的FD-SOI技术上将节点推进到10nm。到了7nm之后,沟道上的的“门”就会上去控制,这就亟待一种全新的晶体管架构。

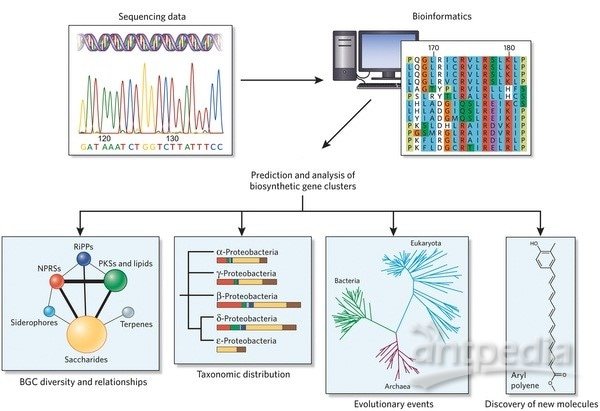

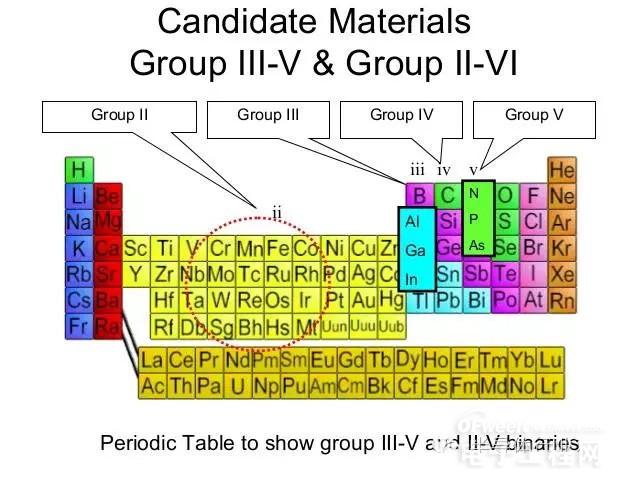

7nm上的一个领先竞争者就是高电子迁移率的FinFet,也就是在沟道上使用III-V 材料的FinFet。III-V族 FinFET则可能会在PFET时采用锗(Ge)作为沟道材料,在NFET时采用InGaAs作为沟道材料。

锗无疑会是一个好选择。由于III-V族本身的特性,我们还需要在上面花费更多功夫。

实际上,III-V族材料已经受到了很多的关注,且可能会在5nm的时候推出。而在7nm的时候,锗和III-V族材料会是最有可能的竞争者。但是这些材料的窄能带隙也会给低漏电的晶体管带来麻烦。为此,对III-V族材料的期待从7nm迁移到5nm。但这并不排除近期会在源极和漏极上使用这种材料。

因此,由于III-V族 FinFET的可能延期,7nm还会采取什么样的方式去实现呢?IMEC考量了几个晶体管选择,得出了环绕栅极场效应晶体管、量子阱FinFET和SOI FinFET(应该是指UTB-SOI)三个答案。考虑到基本的CMOS器件遵从静电学,而环形栅极则是一种把栅极放置在沟道四面的结构。从某种意义上来看,在环形栅极的制程里,你需要从底部切断Fin。这样的话,在制作栅极到电介质时,沟道的下部会被填满。而现在这个位置只是纳米线,IMEC表示。

当然,SOI也是可取的,量子阱也是个不错的选择,你可以搭建一个有效的能量区域去关闭漏电通道。

关于7nm时候的沟道材料的选择,IMEC将其范围缩窄到两个:一个是由80%锗组成的PFET;一种是25%到50%混合锗的FET和0到25%混合锗且带有strain relaxed buffers(这里怎么翻译,应变弛豫缓冲层?)的NFET。最完美的选择材料是锗无疑。

硅器件的运行电压是0.8和0.75V,而锗器件的工作电压是0.5V,因此从静电学的角度看,你的确找到了你所需要的材料。毫无疑问,使用锗让你降低了Vdd,进而降低了功耗。

而在7nm之后,业界也给出了几种晶体管选择,如上面提到的环形栅极、量子阱、SOI FinFET,还有III-V族FinFET和垂直纳米线。IMEC表示他们正在考量垂直纳米线的方方面面。同时他们也在探索如何生长沟道,在集成方案的时候也在衡量是先使用沟道还是后使用沟通。

存在的挑战

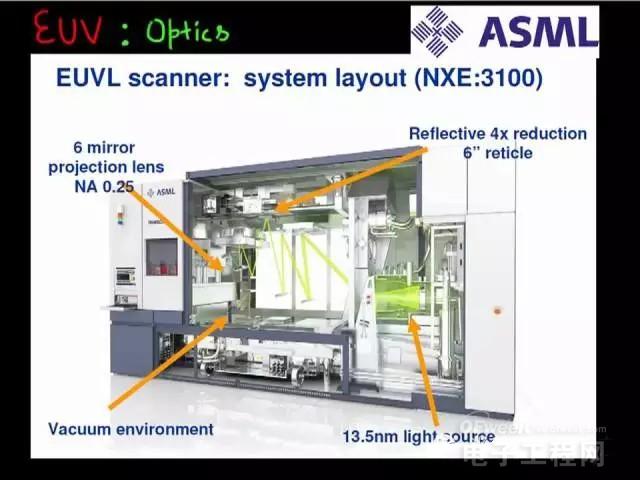

在10nm之后,半导体工业面临很大的挑战,首当其冲的是光刻技术。为了降低曝光的花费,IMEC的CMOS合作伙伴希望在7nm的时候用上EUV光刻。但由于电源功率多种原因的影响,EUV已经错过了很多个市场窗口,并且数次延期。根据媒体报道,截止今年八月:

半导体顾问公司的分析师RobertMaire认为EUV真能应用于量产应该是大约在2020年,在5nm时。近期TSMC公布它的计划也是在5nm节点。

Maire说英特尔可能会有不同的观点,它采用EUV设备在7nm,因为今年下半年它有可能进入10nm(Intel的10nm接近于代工厂的7nm,7nm接近于代工厂的5nm)。

因为现在16/14nm节点时通常采用两次图形曝光技术,如果EUV成功量产,可以避免在10nm及以下时要采用三次或者四次图形曝光技术,成本上可大幅的节省(原则上应该是由于EUV分辨率高,不需要拆分Mask成为几张子Mask,从而节省了Mask成本,同时节省了制造时间)。

从20nm节点开始要采用两次图形曝光技术,芯片制造商人为的把工艺节点分成两类,如20nm及10nm都是过渡节点,相对工艺寿命短,而28nm,16/14nm及7nm可能是长寿命节点。

ASML的市场部总监Micheal Lercel说EUV系统量产需要安装250瓦光源,保证每小时125片,而现在的光源是125瓦,只能每小时85片,ASML正在实验室中研发210瓦光源。

目前大于200瓦的EUV光源有两家供应商,分别是ASML的Cymer及Gigaphoton。两家供应商都认为未来500瓦光源有可能性。

目前用于EUV掩膜保护的Pellicle只能承受125瓦的热负荷,离开250瓦的目标尚有一段距离。

由于EUV光刻胶它的工作模式是采用反射的二次电子,不同于通常的193nm光刻胶,因此尚需要突破。

目前EUV光刻的成本非常接近于三次图形曝光技术。

ASML希望它的EUV系统能有大於90%的uptime,但是目前在4周工作周期中它的uptine大於80%。而ASML计划2018年时它的EUV设备的产能再扩大一倍达到年产24台,每台售价约1亿美元,目前芯片制造商己经安装了8台,正在作各种测试。(uptime不懂)

设备从研发到量产有很大的差别。光源系统的可靠性要求十分高,即便系统工作在真空环境下要求每秒能击中50,000次融化的锡珠(这句话读不懂。。。。)。因此新的光源体积很大,相比之前的准分子激光源更为复杂,它的尺寸如同电冰箱一样大,工作在洁净厂房中。

业界都希望在7nm的时候有EUV和多重曝光加持。并将图层的pitch降到21nm,这其实比EUV本身能够分辨的最小pitch还低,要将如Fin等的图层做到21nm,那就需要EUV加上双重曝光去实现。毫无疑问,在未来,业界会将推动这些技术的全部全方位发展。

如果EUV折戟,那么业界就会将目光转向193nm沉浸和多重曝光。有业界人士表示,如果EUV没准备好,那么Fin就会使用spacer patterning(侧墙转移技术)。我们也很清楚的知道,spacer patterning需要沉积和刻蚀,如果你想重复这个过程,那么你就需要经过两次浸没式光刻,但这样做的话,成本会显著提升。有时候你还需要做第三次,这样的话成本就更高了。

Patterning只是众多难点中的一个,到了7nm之后,你就有了22nm, 14/16nm, 和10nm FinFET,那就是拥有了三代的FinFET 技术。随着你缩小FinFET的尺寸,你会在沟道的栅极耦合上面临与平面型器件相同的问题。

因此到了7nm,业界需要寻求一种能降低栅极长度和维持高性能的新晶体管技术。应用材料晶体管技术部门的高级总监Brand认为环形栅极场效应管是最有效的选择。他表示未来他将押重注在环形栅极场效应管上。