漫谈半导体工艺节点(三)

Brand指出,环形栅极场效应管并没有想象中那么不稳定,它其实非常实用,你甚至可以把它当做FinFET的改良版。实际上它只是在沟道上增加了几个面。Brand不确定环形栅极场效应管是否能在7nm实现,或者在5nm实现,这一切都取决于业界的进展。更决定于公司在降低栅极长度上是否足够激进。

环形栅极场效应管需要复杂的纳米线架构,但这个在精度控制上面并没有验证。这中间还会面临很多挑战,其中一个就是接触电阻。

至于花费方面,从Intel的22nm开始,和传统的Planar相比,在工艺流程中使用FinFET需要额外付5%的费用,因此在工艺制程中你可以轻易引进一些“破坏性”的新技术。如果是用环形栅极场效应管做水平图层,很多步骤都是和以前相同。当然,也会添加一些类似epi(外延)、selective removal(选择性刻蚀or选择性去除) 和 ALD等工序。

如果几十年后,业界用平面晶体管设计和生产芯片,这又是另一个课题。目前看来,IC设计和制造群体必须拥抱FinFET。在7nm的时候,晶体管势必会带来翻天覆地的变化,届时相关的设计也会被革新。

正是基于这个原因,有些人坚信业界应该扩展FinFET。环形栅极和其他架构也会拥抱晶体管的变化,做出相应的转变。从平面晶体管到FinFET的转变,设计和制程发生了重大的改变。因此除非是强烈需求,否则业界应该不会轻易切换到其他其他架构。

10nm之后,也会有很多方式去扩展FinFET,例如从Fin过渡到三五族、锗,或者将Fin延伸,作为FinFET技术的自然扩充。但这项技术的因素并没全部搞定(翻译带商榷)。例如关于三五族半导体,我们还多东西需要去探索,但我们最终肯定能够到达“终点”。但我们是否会在7nm实现,那就不一定了。

毫无疑问,芯片行业正在全速迈向7nm和5nm,TSMC也展望在2018年推出7nm芯片。台积电和其他业者也在跟进环形栅极晶体管的研究,但并没有什么是一成不变的,因为如果下错注了,损失会非常惨重。因此台积电表示会衡量所有的方式。

从目前的情况看来,硅基的FinFET会在10nm的时候后继乏力,因此行业都在探索新型的晶体管架构(前文有提到)。

另外有一点需要注意的是,7nm和5nm,BEOL是在衬底上增加物质(增加材料 这样翻译是否更合适?),通过叠加金属和钝化层来完成互联功能)对于延续摩尔定律会产生很重要的作用,而实际上,BEOL是远远落后于晶体管制造前端和中端的工艺,它会随着节点的演进导致RC延迟呈现指数级增长。应用材料的专家表示,我们未来会在头发那么点的宽度里填充超过1000个内部连接。因此在未来我希望从我们的终端客户那里了解到他们对于后段材料的需求。因为他们普遍反映后段工艺的节奏没跟上。

业界正在寻找新的方法,希望在10nm的时候降低RC延迟。至于7nm节点,从业者正在探索新的工具和材料突破。行内人都认为到7nm的时候,市场是完全开放的,并没有什么是必然的。

行业也在寻求新的材料去改变传统的架构,如Co、Mn和Ru,除了材料以外,业界也在其他方面探求解决办法,例如碳纳米管、石墨烯。业界人员也应该跳出这种固有思维,因为除了材料之外,还有很多其他问题亟待解决,例如为了避免RC延迟,芯片制造商需要追求解决办法,例如2.5D和3D芯片,垂直纳米线等等。

光刻和材料问题

在一个设备中,有两种类型的BEOL连接线,一种是intermediate,一种是global。intermediate解决设备中低级别的连接问题。而和以往一样,RC延迟的问题是与连接 intermediate层的global 线相关的。从20nm开始,芯片制造商在制造芯片过程中增加了另外一种线,加大了芯片的复杂性。那就是MOL(middle-of-the-line),(我了解的是MOEL,请按原文,应该是增加了middle end of the line,MEOL,或者就是前文的MOL,MEOL引入了Local Connect,增加区部互联性) 这就在设计中增加了区域互联(这里应该是就是前面的Local Connect)。

在BEOL那个阶段,有非常多的步骤,但主要可以分成两个类别,那就是patterning 和 dual damascene。最初,在整个流程里面,芯片架构的每个层级必须曝光布线图。为此,芯片制造商在FEOL(FEOL完成的是器硅片上器件结构的过程,比如做栅,做源漏,这个过程对设备的要求是很高的,对洁净度的要求也很高)和BEOL使用193nm沉浸和多层曝光。

BEOL的布线在每个节点的花费是很大的,并且极具争议性的。其中金属层和连接层的争议是最大的。如果用193nm沉浸去实现,就有点艰难,这就为什么对EUV有极大的需求(后段工艺的前几层是工艺中对光刻要求最高的几层,最高精度的几层需要拆分mask)。

7nm之后,业界都选择EUV为后段的pattern,EUV会把BEOL带回到单次曝光的年代,如果EUV的产量能够达到每小时150片晶圆,BEOL的成本将会降低30%。但就目前看来,EUV的进度没跟上。如果EUV真的错过了7nm,芯片制造商必须去寻找新的光刻解决方案。

EUV光刻的缺席会带来更多的连线层需求,这无疑就增加了成本。

而内部连接,现在也面临各种挑战,例如高电流密度,这会给芯片设计和生产带来影响。

随着节点的演进,人们探讨过很多材料,例如在65nm的时候,人们就研究了钌,相对于钴而言,它有很好的性能,能充当重要的角色。另外由于钌能够使铜回流,因此你可以想想一下利用PVD来满足内部连接。

钌当然也是有缺点的,例如很难抛光,对于制造来说,钌是非常不友好的。

其他的选择

半导体业界一直在探讨各种解决办法,但经常会碰到失败或者昂贵的问题。例如业界曾经为7nm探讨过SAV(self-aligned via)规划,这个能够解决在紧密pitch情况下的via-to-metal短路问题,但SAV有着对不准的大挑战(对光刻的套准精度要求极高)。

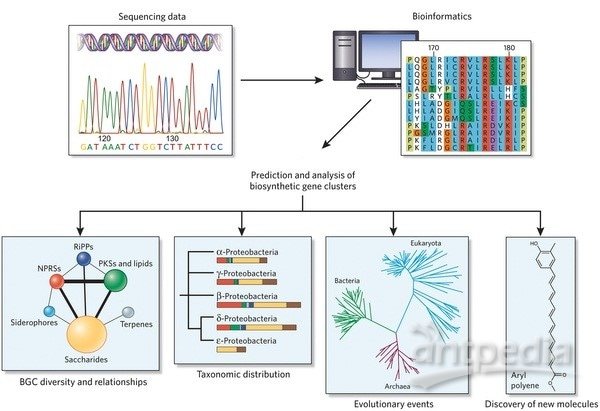

业界也在探讨碳纳米管和石墨烯在5nm时候的功效。从工艺流程上看,碳纳米管是利用CVD生长的。然后在平坦化制程期间,会用到一种混合物封装去保护其架构。

而在5nm,IMEC也开发了一种垂直纳米线晶体管,它能够使用常用材料或者碳纳米管实现内部连接。其实在5nm或者以后,除了垂直,我相信行业没有其他方法可选。

除了垂直纳米线,我们还有其他技术可供候选,那就是三维芯片。其中包括了在每个三维芯片上加上堆栈、对其和连接尖端晶体管。在最小配线幅度下,monolithic 3D 芯片能够提供的连接是2.5D/3D TSV的一千倍。

CEA-Leti,作为这个技术的主要推动者,指出了三维芯片的挑战,那就是顶部的晶体管热平衡需要被限制在一定范围去保护底部的FET。换句话说,那就是业界必须找出600摄氏度下的电子活化技术。于是CEA-Leti去研究了包括激光退火工具。这个工具只有308nm的波长,且还有短脉冲。

初次之外,还有很多传统的方法,例如堆叠芯片。平面型期间的电阻系数问题会加速使用TSV技术开发2.5D和3D芯片。

无需要多讲,业界正在为7nm选择更好的方案,大家有什么样的观点呢?