数字电路之数字集成电路IC(二)

注意误操作和扇出

在连接“标准逻辑IC”时,需要考虑一个输出最大可连接的IC数量。

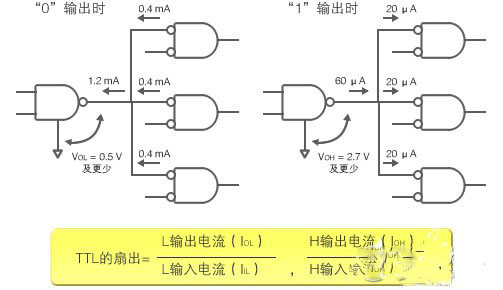

在TTL IC中,可连接IC的数量受到输出电流的限制,我们把允许连接的IC上限个数称为扇出。只要想起TTL IC是由双极性晶体管构成的,就能容易地想象出开关切换时是需要电流的。TTL IC的扇出可以通过输出电流除以输入电流来求出(图3)。需要注意的是如果连接的IC个数超过了扇出数,将无法保证输出的逻辑电平。

图3:TTL IC的扇出

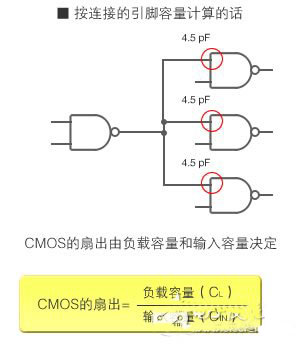

由于CMOS IC的输入引脚中几乎没有电流,因此无法根据电流计算它的扇出数。需要根据负载容量计算(图4)。

在CMOS IC的数据表中,通过传播延迟时间的测量方法明确记载了负载容量。如超过负载容量,传播延迟时间将变长,可能引起误操作,需要注意。

图4:CMOS IC的扇出

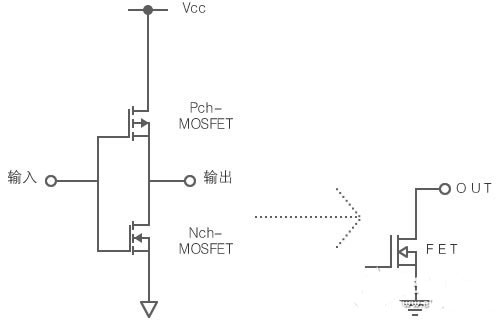

输出线之间连接,漏极开路

漏极开路是指不能输出高电平(High)的FET(如图A右图)。在漏极开路的电路中,不存在通常CMOS IC输出段(如图A左图)中和VCC相连的MOSFET,所以,无法输出高电平。只能输出Low或高阻抗(输出端和电路是断开的,是一个无法输出电流和电压的状态)。

在高阻抗的情况下,由于输出不稳定,因此需要通过电阻和电源相连,把输出端固定在High电平下使用。该电阻称为上拉电阻。

由于上拉电阻连接的电压不需要与电源电压相同,因此可以连接逻辑电平不同的IC。

图A:CMOS输出与漏极开路输出

组合逻辑电路

逻辑电路中,只通过输入信号的组合方式决定输出的逻辑电路称作“组合逻辑电路”。

相反,内部拥有记忆电路和同步电路,只通过输入信号的组合无法决定输出的逻辑电路被称作“时序逻辑电路”。

本期只对前者“组合逻辑电路”进行讲解。

“组合逻辑电路”是通过组合多个AND、OR、NOT、XOR等逻辑门而构成的。可以理解为用多个逻辑门的排列就能实现多种功能的电路。

首先让我们来看看“组合逻辑电路”的代表元器件,多路复用器和解码器。

可选择输出信号的多路复用器

多路复用器是可以从多个输入信号中选择一个输出信号的信号切换器。可以通过自动售货机来想象其工作模式。各种饮料的按钮就是输入信号,当按下选择按钮后,从同一出货口可以拿到各种饮料。

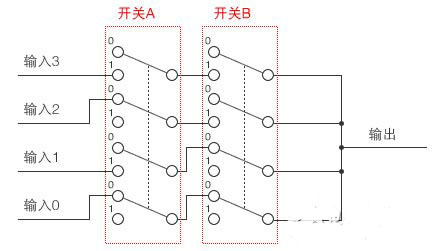

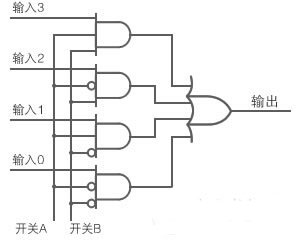

如果用开关说明多路复用器的工作原理,如图5所示。开关A包括4个纵向联动开关。开关B也是一样。那么,当开关A为0,开关B也为0时,可以看到输入0连接到输出上,也就是输入0的信号被输出。同样,当开关A为1,开关B为0时,输入1的信号将连接到输出上。当开关A为0,开关B为1时,输出2的信号将连接到输出上。当开关A为1,开关B为1时,输入3的信号将连接到输出上。也就是说,可以通过开关A和开关B从4个输入中选择一个输出。这就是实现信号切换的多路复用器电路。

图5:用开关构成的多路复用器

多路复用器用逻辑电路表示的话,就象图6所示,只需要AND和OR就可以实现。AND部分进行判断,OR部分用于选择一个信号输出。

图6:用逻辑电路构成的多路复用器

判断输入的解码器

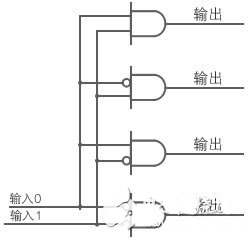

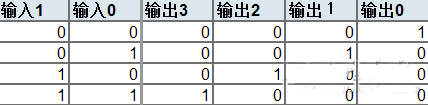

请看解码器的真值表(图8)。由该表可知, 2个输入信号可通过4个输出信号中的一个输出。比如当两个输入为二进制时,让4个输出信号分别对应十进制的0、1、2、3,就可以认为这是一个将二进制解码为十进制的电路。

图7:用逻辑电路构成的解码器

图8:解码器真值表

除此之外,还有比较器、加法器(全加器/半加器)、乘法器、减法器、桶形移位器等多种“组合逻辑电路”。其中大多数都是应用多路复用器和解码器制作而成的。但是,如果只是应用而不做改善的话,将出现电路冗长等问题,所以,需要简化并压缩电路。