上海交大毛志刚等JSSC上连发两篇论文 MPAM技术提升传输可靠性

近日,上海交通大学电子信息与电气工程学院微纳电子学系教授毛志刚、教授何卫锋团队在集成电路设计领域的国际顶级期刊《IEEE固态电路杂志》(IEEE Journal of Solid-State Circuits,简称JSSC)上连续发表两篇学术成果。

研究内容

TICA:Timing Slack Inference and Clock Frequency Adaption Technique for a Deeply Pipelined Near-Threshold-Voltage Bitcoin Mining Core

TICA:面向近阈值、深度流水SHA256电路的时序裕量推测及自适应压缩技术

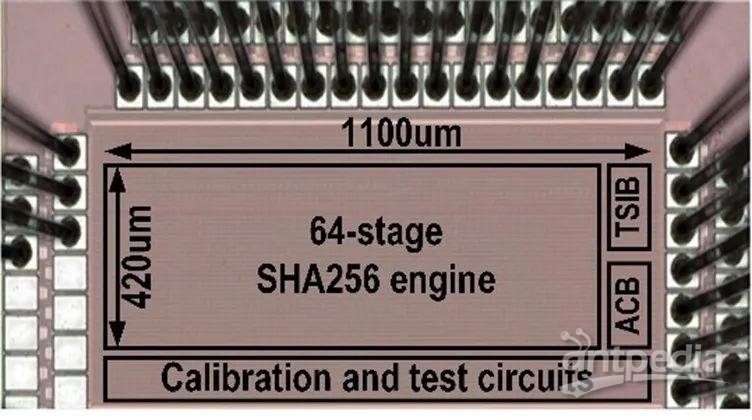

TICA-based SHA256加解密芯片显微图

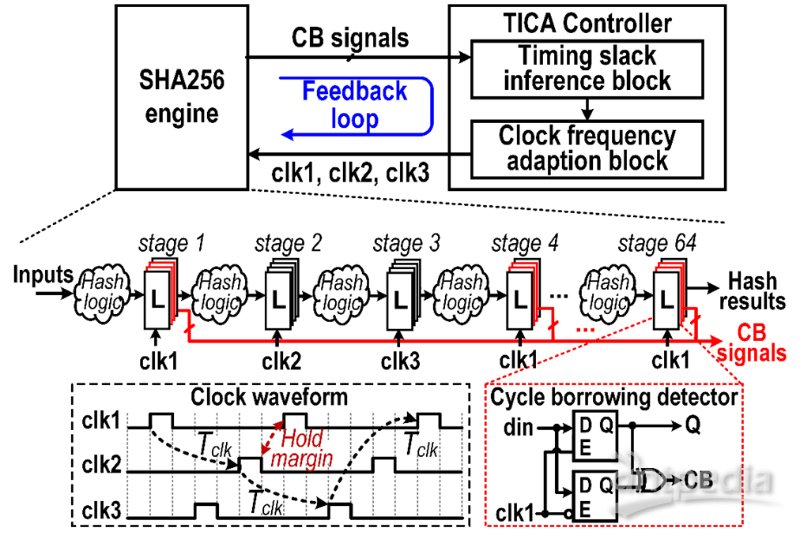

TICA-based SHA256加解密芯片顶层架构图

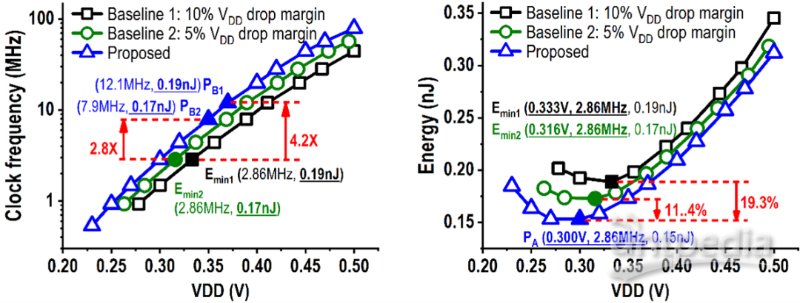

芯片测试所得的性能和能效收益

近阈值电路由于具有高计算能效的优势而得到了广泛关注。然而,在低电压下,剧烈的工艺、电压、温度(PVT)波动导致芯片需要设置极大的悲观时序裕量来保证其功能的正确性,由此制约了电路性能和能效的提升。

针对上述问题,研究团队提出了一种时序裕量推测与自适应调节(Timing slack inference and clock frequency adaption, TICA)技术。这一技术利用稀疏插入的时间借用事件检测单元来感知电路PVT波动的实时变化,并动态推断电路的运行时时序裕量。在此基础上,通过自适应调节电路的时钟频率,实现了对悲观时序裕量的有效压缩。

研究团队将TICA技术应用于基于深度流水线结构的SHA256加解密电路,并采用28纳米CMOS工艺完成了芯片的原型开发。测试结果表明,芯片的工作电压范围可达0.21V至0.9V的宽电压区间,0.3V下的性能收益为4.2倍,能效提升19.3%。

论文的第一作者为电院微纳电子学系博士生李婕妤,通讯作者为其导师何卫锋。

论文链接:

A Metastability Risk Prediction and Mitigation Technique for Clock-Domain Crossing with Single-Stage Synchronizer in Near-Threshold-Voltage Multi-Voltage/Frequency Domain Network-on-Chip

https://ieeexplore.ieee.org/document/10159987

面向近阈值多电压、时钟域片上网络的低延迟跨时钟域亚稳态预测与消除技术

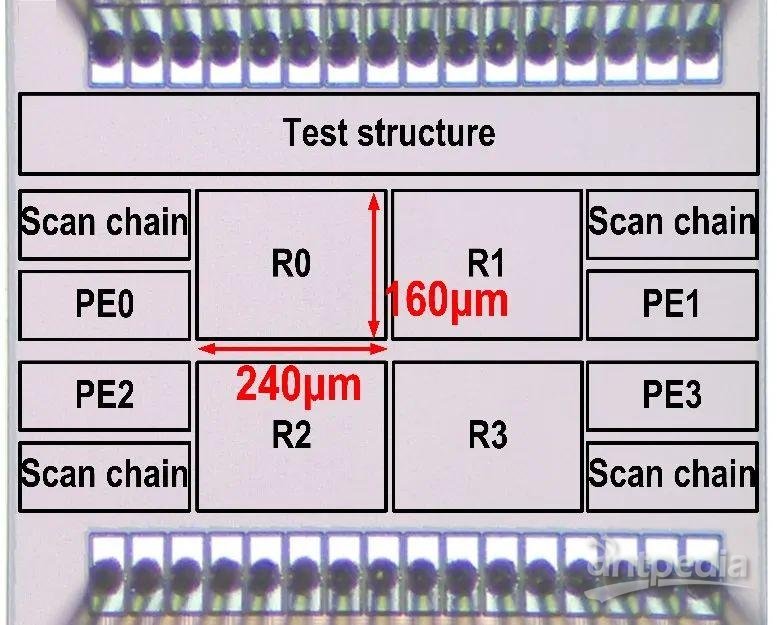

基于MPAM的片上网络芯片显微图

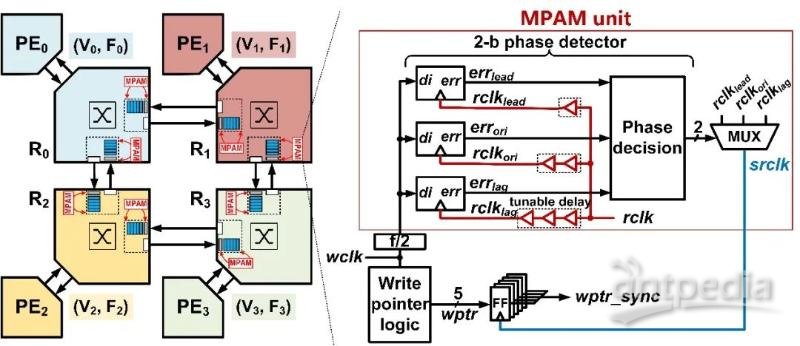

基于MPAM的片上网络架构

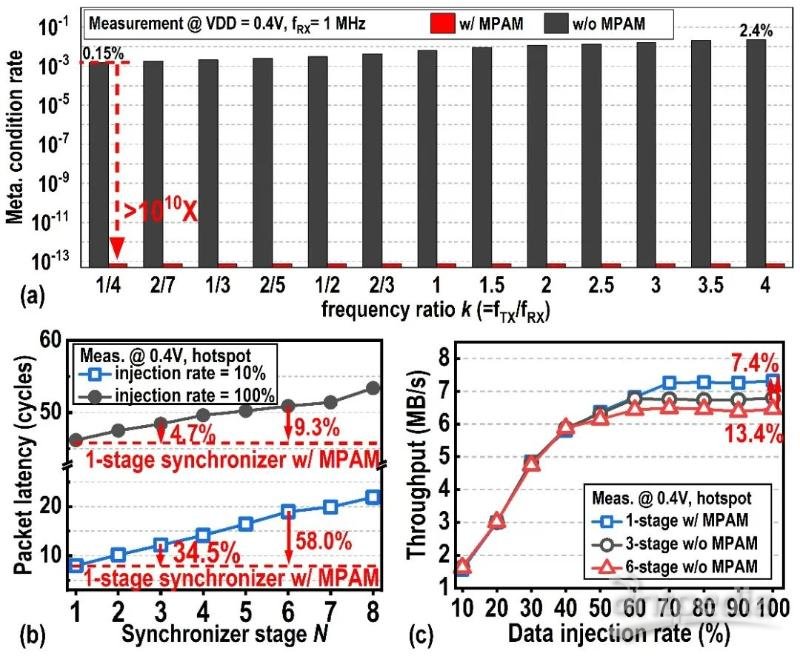

基于MPAM的片上网络在亚稳态风险概率、延迟和吞吐率上的收益

为了提升计算系统的性能和能效,动态调频调压、全局异步局部同步等低功耗技术被广泛应用于多核/众核处理器中。在此背景下,片上系统中核与核之间的跨时钟域数据通信面临着亚稳态导致的可靠性问题。虽然基于多级同步器的传统方法可以有效降低亚稳态出现的概率,但其存在着同步延迟增加、数据传输效率降低等问题,不利于多核/众核处理器的性能提升。

针对上述问题,研究团队提出一种亚稳态风险预测与消除(Metastability Risk Prediction and Mitigation, MPAM)技术。这一技术利用基于三相时钟的亚稳态风险预测机制提前推测跨时钟域互连中的亚稳态风险,并通过动态时钟相位切换机制消除即将到来的亚稳态风险,从而有效规避了跨时钟域数据传输中的亚稳态风险,实现了基于单级触发器的低延迟跨时钟域数据同步。

研究团队将MPAM技术应用于包含四个独立电压域和时钟域的2×2片上网络(Network-on-chip,NoC)中,并采用40nm CMOS工艺进行了芯片原型开发。测试结果表明,MPAM技术能够将亚稳态风险降低十个数量级、数据传输延迟降低58%、片上网络数据吞吐率提升13.4%、系统能效提升8.6%。

论文的第一作者为电院微纳电子学系博士生林初雄,通讯作者为其导师何卫锋。

论文链接:https://ieeexplore.ieee.org/document/10159987

关于JSSC

IEEE固态电路期刊(JSSC)是国际集成电路领域的旗舰期刊,旨在发布集成电路设计领域的最新技术进展和纪录性成果,代表着当前学术界和工业界的最高技术水平。

集成电路产业关系到经济建设、社会发展、国家安全,战略意义重大。近年来,上海交大电院微纳电子学系以探索国际前沿芯片设计技术为己任,先后在片上网络芯片、低功耗数模接口电路和高能效专用加速器等方面分别取得突破,成果陆续发表在JSSC上。

-

焦点事件

-

焦点事件