高速转换器原理及作用(四)

实现

实现宽带混合信号系统不仅仅要选择正确的数据转换器——这些系统可能对信号链的其他部分有着严苛的要求。同样,挑战是在较宽的带宽范围内实现优秀的动态范围——使更多的信号进出数字域,充分利用数字域的处理能力。

宽带和信号调理—在传统单载波系统中,信号调理就是尽快消除无用信号,然后放大目标信号。这往往涉及选择性滤波以及针对目标信号微调的窄带系统。这些经过微调的电路在实现增益方面可能非常有效,而且在某些情况下,可以利用频率规划技术来确保将谐波或其他杂散排除在带外。宽带系统不能使用这些窄带技术,而且在这些系统中实现宽带放大可能面临巨大的挑战。

数据接口—传统的 CMOS 接口不支持大大超过 100 MHz 的数据速率——而且低电压差分摆幅(LVDS)数据接口运行速率达 800 MHz 至 1 GHz。对于较大数据速率,我们可以使用多个总线接口,或者使用 SERDES 接口。现代的数据转换器采用的是最高速率达 12.5 GSPS 的 SERDES 接口(规格见 JESD204B 标准)——可以用多条数据通道来支持转换器接口中分辨率和速率的不同组合。这些接口本身可能十分复杂。

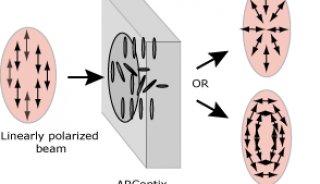

时钟接口—就系统中使用的时钟的质量来说,高速信号的处理也可能十分困难。时域中的抖动 / 误差会转换成信号中的噪声或误差,如图 5 所示。在处理速率大于 100 MHz 的信号时,时钟抖动或相位噪声可能成为转换器可用动态范围的一个限制因素。数字级时钟可能无法胜任这类系统,可能需要使用高性能时钟。

图 5. 时钟误差变成信号误差的方式

结论

走向更宽带宽信号和软件定义系统的步伐不断加快,业界不断推陈出新,涌现出构建更好、更快数据转换器的创新方法,将带宽、动态范围和功效三个维度推上了新的台阶。