毫米波收发器系统硬件介绍(二)

PXI Express机箱

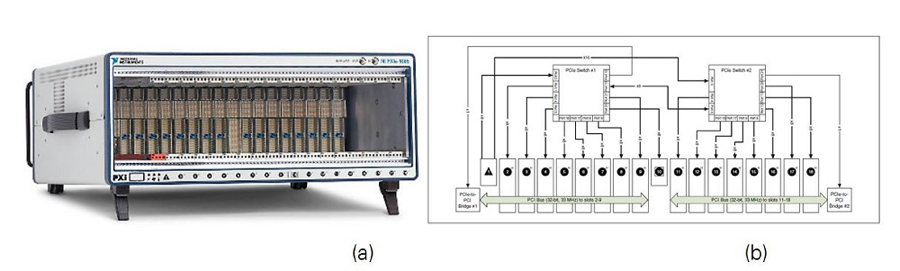

原型验证系统以PXIe-1085机箱为基础。 机箱包含不同的处理模块,并提供电源、互连功能以及定时和同步基础设施。 这款18槽机箱的每个插槽均搭载了PCI Express(PCIe)第3代技术,适用于高吞吐量和低延迟应用。 机箱可提供4 GB/s的单槽带宽和24 GB/s的系统带宽。 PXIe-1085采用双开关背板架构,正如图3系统图所示。由于灵活的PXI设计,在创建高通道数系统时,多个机箱可通过菊花链方式或星形配置连接在一起。

高性能可重配置FPGA处理模块

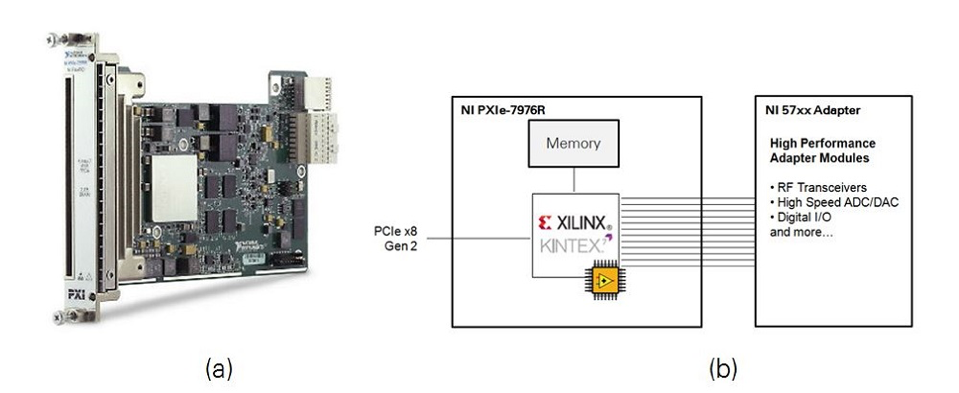

所有SDR均需要软件与计算元件来组成物理层。 这款毫米波原型验证系统采用单槽FlexRIO模块,为PXIe机箱中添加了灵活的高性能处理模块,该模块可使用LabVIEW进行编程。 PXIe-7976R FlexRIO FPGA模块可独立运行,提供了可自定义的大型Xilinx Kintex-7 410T,通过PCI Express Generation 2 x8 连接至PXI Express背板。 此毫米波收发器系统可根据不同的配置,将不同处理任务分配给不同的FPGA,配置可通过软件进行设定。

图4: PXIe-7976R FlexRIO模块(a)与系统框图(b)

用于高传吞吐量应用的高性能 FPGA

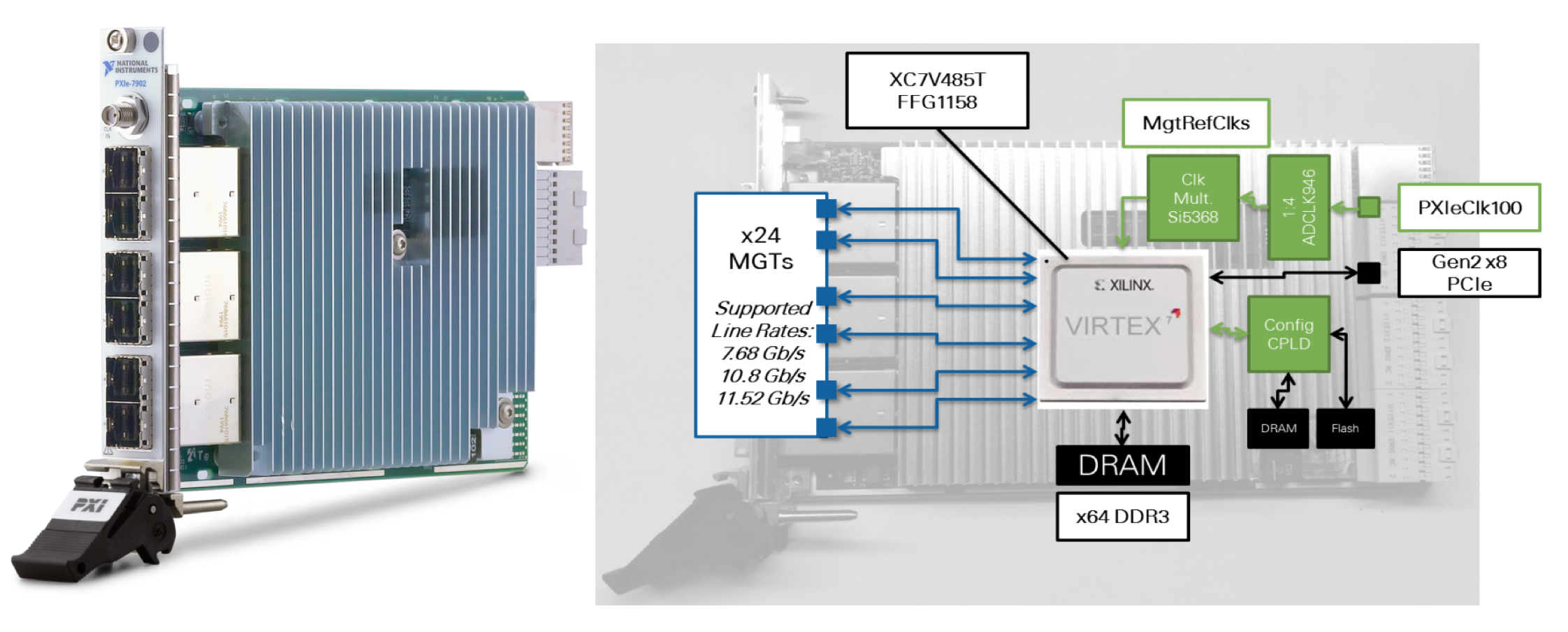

NI PXIe-7902 FPGA模块是基于Xilinx Virtex 7 485T构建的功能强大的处理模块。 大型FPGA适用于处理计算密集型应用,例如毫米波物理层。 此模块能以PCIe gen 2x8的速度在PXIe机箱的背板之间传输数据。 对于需要更快数据传输率的应用,PXIe-7902 还提供了由 24 个GB级收发器 (MGT)组成的6 个miniSAS HD 前端面板连接器。 MGT可连接至其他PXIe-7902或其他DAC/ADC模块,使多信道基带信号具有高达2 GHz的实时宽带。

图5: PXIe-7902R FPGA模块(a)与系统框图(b)

超宽带DAC与ADC

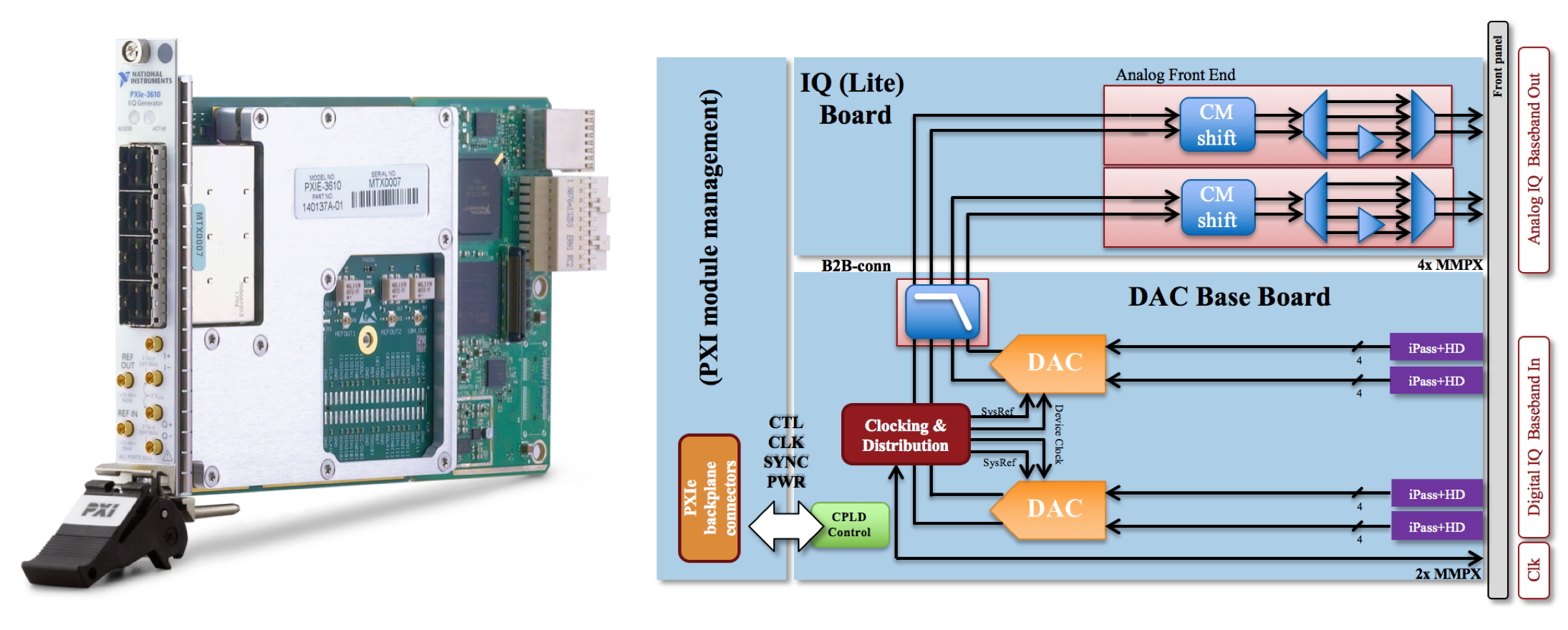

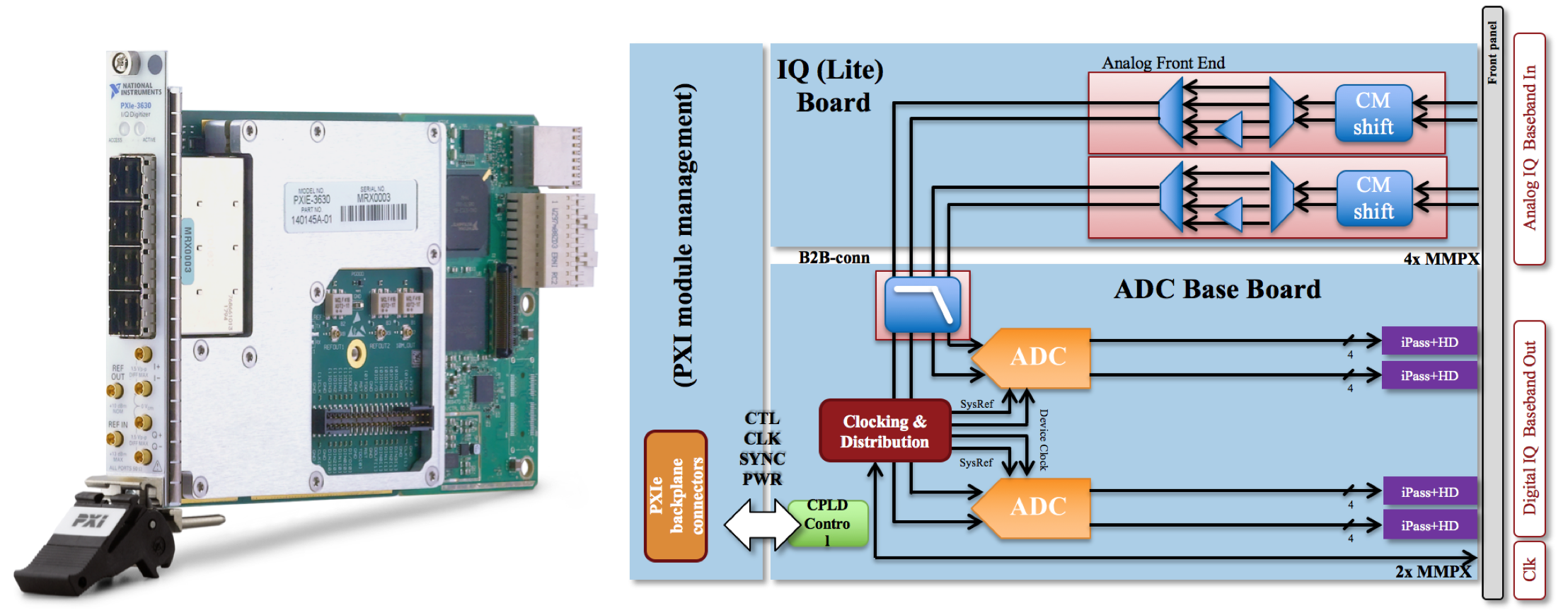

图6为 PXIe-3610 DAC,图7为PXIe-3630 ADC。两者均可通过4个MCX前面板接头来连接模拟基带差分I/Q对。 这些模块可连接起来,组成一个基带环回测试系统,并连接至 PXIe-3620 IF模块或第三方基带硬件。 表1为基本性能信息。如需查看详细的性能信息,请查看毫米波收发器系统数据表。

![]()

表1: PXIe-3610与PXIe-3630的基本性能规格

图6: DAC模块与程序框图

图7: ADC模块与与程序框图

12 GHz IF模块

PXIe-3620 LO/IF模块能以高达2 GHz的带宽分别处理一组传输链与一组接收链。 NI PXIe-3620通过将输入信号与集成式LO组合,可将基带信号上变频10.5至12 GHz之间的软件可编程IF。 针对接收部分,NI PXIe-3620可接收10.5至12 GHz的输入IF ,并将其转换为基带信号。 该模块具有内部增益控制功能,并可传输高达7 dBm的信号和接收20 dBm的信号。 PXIe-3620 还提供适用于NI 3647与 NI 3657毫米波电站的LO参考信号。 LO/IF模块可接受外部LO信号,也可针对其他IF模块驱动LO信号,以在 MIMO 拓扑中同步多个发射器/接收器数据流。 差分I/Q可通过设备前面板的MXC连接器访问。

图8: PXIe-3620 IF模块