接地与EMC的分析设计(二)

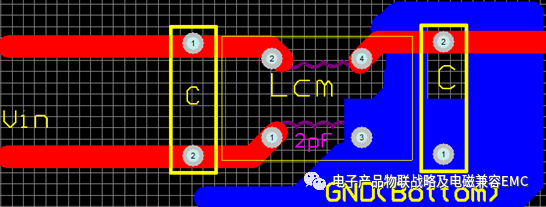

当电子线路中有共模电感的滤波设计时,前后级进行PCB铺地铜设计时TOP层的走线与BOTTOM底层的PCB铺地就会存在耦合电容Cp;高频的骚扰信号就会通过耦合电容影响共模电感的噪声阻抗性能;等效电路如下:

比如系统的设计LCM器件的杂散电容为2pF;其谐振频率点在4MHZ左右;进行PCB的铺地铜的设计由于PCB的布线,其输入的走线与PCB的铺地铜带来有6pF的耦合电容参数;分析如下:

在其LCM的谐振点后就会降低其阻抗值-如上图的频率&阻抗特性曲线参考数据;在进行EMI测试时就会带来高频>4MHZ的高频EMI的问题!

在进行PCB双面板布线铺铜地的设计时;在某些电路设计中改进PCB布局及走线就可以降低高频的EMI电磁干扰;简单优化的PCB设计参考如下:

注意:如果接地层存在噪声耦合源,则接地层不应靠近敏感输入电路。

对于双面板的系统有时钟信号是很普遍的;系统晶振时钟频率高,干扰谐波能量就强;干扰谐波除了从其输入与输出两条布局布线传导出来还会从空间辐射出来,若布局布线不合理,很容易产生很强的尖峰噪声辐射问题,因此在PCB 板布局布线时对晶振和CLK 信号线布局非常重要,高频时钟信号需要能镜像回流完整的铺地铜的设计是很关键的。

时钟源的布局布线简单说明如下:

A.对于有源晶振:耦合电容应尽量靠近晶振的电源引脚,位置摆放顺序:

按电源流入方向,依容值从大到小依次摆放,容值最小的电容最靠近引脚。

B.晶振的外壳必须接地,可将晶振信号源包地设计;防止向外辐射,也可以屏蔽外来信号对晶振的干扰。

C.晶振下面不要布其它走线,保证完全铺地,同时在晶振的300mil范围内不要布其它走线,防止晶振噪声源耦合到其它布线、器件等影响性能。

D.时钟信号的走线应尽量短,晶振不要放置在PCB板的边缘!

如果电路板边缘有复位及数据&地址信号线等等,PCB的板的边缘都需要进行铺地铜的设计;保证关键信号线的地回流路径的镜像对称性设计。

因此,对于PCB双面板的铺铜地不是每个地方按面积来铺设的,铺地要有目标的去铺设才能有好的作用,不正确的铺地设计反而会恶化系统的EMC性能。

更多设计应用实践及技术交流;请关注阿杜老师!

杜佐兵

电磁兼容(EMC)线上&线下高级讲师

杜佐兵老师在电子行业从业近20年,是国家电工委员会高级注册EMC工程师,武汉大学光电工程学院、光电子半导体激光技术专家。目前专注于电子产品的电磁兼容设计、开关电源及LED背光驱动设计。

2019年在电源网研讨会和大家一起进行交流!

下一站 东莞,成都,上海,杭州……我将理论与实践分享给大家;

与君探讨,我们不见不散!

如果对我以下的课程(课题)感兴趣,欢迎邀约和大家分享!

任何的EMC及电子电路的可靠性设计疑难杂症;先分析再设计才是高性价比的设计!

实际应用中电子产品的EMC涉及面比较广;我的系统理论及课程再对电子设计师遇到的实际问题进行实战分析!先分析再设计;实现性价比最优化原则!