通过辐射发射测试:如何避免采用复杂的EMI抑制技术...-2

EMI抑制技术:亟需更好的方法

与使用分立式变压器的传统方法相比,将变压器和电路集成到芯片级封装中可减少组件数量,进而大大节省PCB空间,但可能会引入更高的辐射发射。辐射发射抑制技术会使PCB的设计更加复杂,或需要额外组件,因此可能会抵消集成变压器所节省的成本和空间。

例如,在PCB级别抑制辐射发射的一种常见方法是为CM电流形成一个从次级端至初级端的低阻抗路径,从而降低RE水平。要实现这一点,可以在初级端和次级端之间使用旁路电容。该旁路电容可以是分立式电容,也可以是嵌入式夹层电容。

分立式电容是最简单的解决方案,可能是有引线或表面安装组件。它还具有适用于2层PCB的优点,但分立式电容价格昂贵且体积庞大,会占用宝贵的PCB空间,特别是在可能堆叠了多个组件的隔离栅旁。

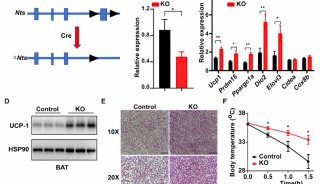

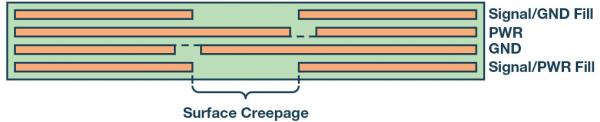

另一个不是很理想的解决方案是使用嵌入式旁路电容,当PCB中的两个面重合时就会形成该电容(图3)。此类电容具有一些非常有用的特性,原因在于平行板电容的电感极低,因此在更大的频率范围内都有效。它可以提高发射性能,但因为需要自定义层厚来获得正确的电容,且PCB需要四层或更多层,所以设计复杂性和成本都会增高。此外,还必须通过隔离的方式,确保内部重叠层的间距满足相关隔离标准所规定的最低距离标准。

图3.中心电源和接地层之间形成的内部PCB旁路电容。

旁路电容还允许交流泄漏及瞬变跨隔离栅从一个接地层耦合至另一个接地层。虽然旁路电容一般很小,但高压高速瞬变可通过此电容跨隔离栅注入大量电流。如果应用需承受恶劣的电磁瞬变,如静电放电、电快速瞬变和浪涌,也必须考虑到这一点。

无论是分立式还是嵌入式,使用旁路电容都不是理想的抑制技术。它虽然可以帮助减少辐射发射,却要以增加组件、采用复杂的PCB布局和提高瞬态敏感性为代价。理想的抑制技术不需要采用旁路电容,因此可以降低成本和PCB设计的复杂性。

免去使用复杂抑制技术的必要

理想情况下,集成的隔离电源组件应该包含降低芯片辐射发射的措施,无需在外部额外增加复杂的措施,即可确保通过系统级辐射发射测试。这样一来,只需将组件放置到2层板上,即可通过严格的辐射发射测试,而无需多次制作电路板。

低辐射发射隔离器

ADI公司的下一代isoPower?系列产品采用创新的设计技术,可以避免产生大量辐射发射,甚至在没有旁路电容的2层板上也不例外。ADuM5020和ADuM5028在以大幅裕量满足CISPR 22/EN 55022 B类限制的同时,可以分别跨隔离栅提供500 mW和330 mW功率。

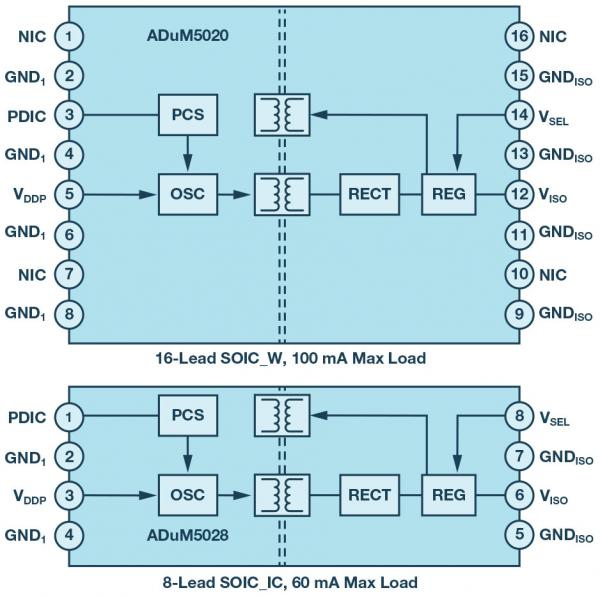

图4.ADuM5020和ADuM5028。

ADuM5020采用16引脚宽体SOIC封装,而对于ADuM5028,可以选择的最小封装是8引脚SOIC。ADuM5020/ADuM5028提供3 V和5 V两种电源选项,以及3 kV rms额定隔离。ADuM5020/ADuM5028提供5 kV rms,可以达到与ADuM5020/ADuM5028相同的功率和辐射发射水平。