芯片毁于噪声:FinFET使噪声效应叠加

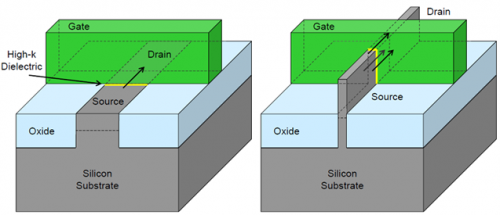

FinFET技术已经成为工艺尺寸继续减小的主要动力。“在可预见的未来,极低的工作电压与漏电流使得FinFET工艺成为CMOS工艺的标准架构,” ANSYS应用工程高级总监Arvind Shanmugavel说道,“但上述优点是有代价的—电源噪声问题变得突出。一方面,10纳米或7纳米的FinFET器件在供电电压(Vsupply)为500mV时也能可靠地工作;另一方面,门限电压(Vt)并没有跟随工艺节点前进而成比例下降。这样一来,电压容限(Vsupply - Vt)急剧减少,设计工程师需要特别注意电源噪声变化。”

平面工艺与FinFET(右)比较

FinFET工艺独有的特性带来了更多的麻烦。“FinFET器件温度更高,因此白噪声会增加,” Cadence电源签核(signoff)产品市场总监Jerry Zhao说,“FinFET器件的三维鳍型结构易聚集热量,这些热量会沿垂直方向传导到鳍型结构上面的走线层。温度升高增加了噪声。”

Naviasky补充道:“FinFET架构没有足够的去耦电容,所以不能将噪声去除干净。有些工艺虽然提供memcap电容,但目前还存在一系列其他的问题。FinFET并没有带来新型噪声,只不过这种技术使噪声问题更加恶化,并由于去耦电容减少而折磨开发人员。”

在1x纳米节点上,不同问题开始相互影响。 “自热效应很糟糕,但遇上电迁移效应,二者叠加产生的影响更坏(一加一大于二)。” Naviasky继续解释,“我们的规则是防止自热增加的温度超过5度,否则等不到处理噪声问题,电迁移问题就会让你招架不及。”