先进的半导体工艺:FinFET简介

FinFET简介

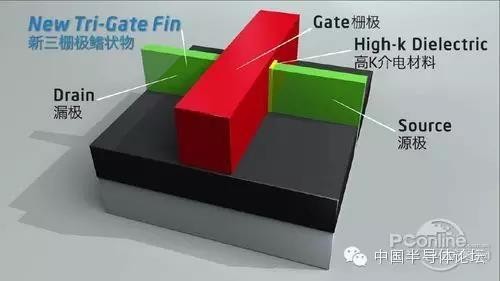

FinFET称为鳍式场效晶体管(FinField-EffectTransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。闸长已可小于25奈米。该项技术的发明人是加州大学伯克利分校的胡正明教授。Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。

发明人

该项技术的发明人是加州大学伯克利分校的胡正明(ChenmingHu)教授[1]。胡正明教授1968年在台湾国立大学获电子工程学士学位,1970年和1973年在伯克利大学获得电子工程与计算机科学硕士和博士学位。现为美国工程院院士。2000年凭借FinFET获得美国国防部高级研究项目局最杰出技术成就奖(DARPAMostOutstandingTechnicalAccomplishmentAward)。他研究的BSIM模型已成为晶体管模型的唯一国际标准,培养了100多名学生,许多学生已经成为这个领域的大牛,曾获Berkeley的最高教学奖;于2001~2004年担任台积电的CTO。

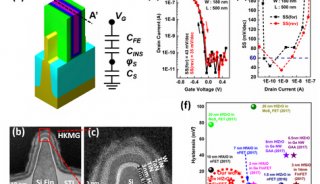

英特尔公布的FinFET的电子显微镜照片

工作原理

FinFET闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。FinFET源自于传统标准的晶体管—场效晶体管(Field-EffectTransistor;FET)的一项创新设计。在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。在FinFET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。[2]

发展状态

在2011年初,英特尔公司推出了商业化的FinFET,使用在其22纳米节点的工艺上[3]。从IntelCorei7-3770之后的22纳米的处理器均使用了FinFET技术。由于FinFET具有功耗低,面积小的优点,台湾积体电路制造股份有限公司(TSMC)等主要半导体代工已经开始计划推出自己的FinFET晶体管[4],为未来的移动处理器等提供更快,更省电的处理器。从2012年起,FinFET已经开始向20纳米节点和14纳米节点推进。

FinFET和普通CMOS的区别

CMOS(ComplementaryMetalOxideSemiconductor),互补金属氧化物半导体,电压控制的一种放大器件。是组成CMOS数字集成电路的基本单元。

在计算机领域,CMOS常指保存计算机基本启动信息(如日期、时间、启动设置等)的芯片。有时人们会把CMOS和BIOS混称,其实CMOS是主板上的一块可读写的RAM芯片,是用来保存BIOS的硬件配置和用户对某些参数的设定。

在今日,CMOS制造工艺也被应用于制作数码影像器材的感光元件,尤其是片幅规格较大的单反数码相机。

SOI和体硅FinFET的比较

本文比较了SOI和体硅FinFET器件在性能、加工工艺及其成本上的差异。如果要使SOI和体硅的FinFET器件具有相类似的性能,体硅FinFET器件的制备流程将更为复杂。在SOI晶圆上,氧化埋层隔离了分立的晶体管,而在体硅器件中,隔离作用则必须通过晶圆工艺来形成。我们将证明,由于体硅FinFET工艺更为复杂,使得器件的差异性达到SOI的140%~160%,并会对制造和工艺控制产生严峻的挑战。虽然SOI基片更为昂贵一些,但更为复杂的体硅FinFET工艺成本的增加大体上已抵消了这部分开销,从而使得在大批量生产时其成本能与体硅工艺大体上相当。

当半导体业界向22nm技术节点挺进时,一些制造厂商已经开始考虑如何从平面CMOS晶体管向三维(3D)FinFET器件结构的过渡问题。与平面晶体管相比,FinFET器件改进了对沟道的控制,从而减小了短沟道效应。平面晶体管的栅极位于沟道的正上方,而FinFET器件的栅极则是三面包围着沟道,能从两边来对沟道进行静电控制。