微波电路设计:PLL/VCO技术如何提升性能? (二)

PLL 改进

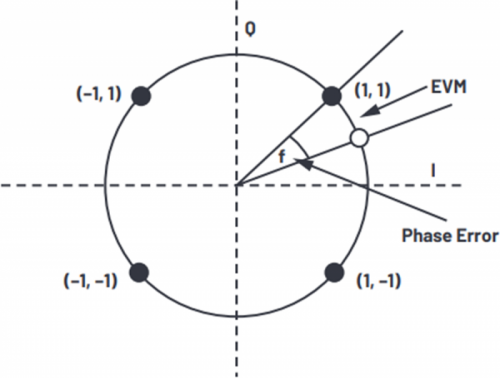

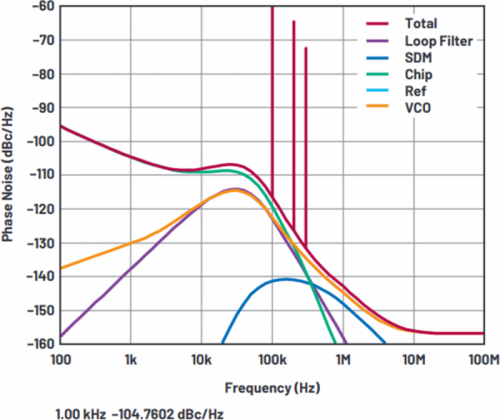

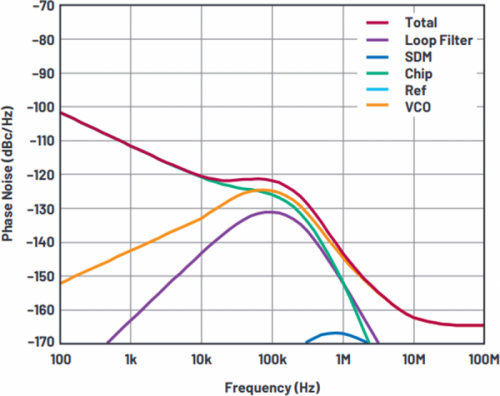

实现更高的数据速率需要具有更低的向量误差调制(EVM)速率(图 4),这主要取决于窄带无线应用中 PLL 频率合成器的带内相位噪声贡献;使用 200kHz 信道栅提供 1.8GHz 输出需要很高的 N(9000),因而 N 分频器的 20log(N)贡献会在频段内产生严重影响。高阶调制速率(例如 64QAM)需要更低的 EVM,这会推动开发、采用和部署小数 N 分频频率合成器,比如 ADF4153A 和 ADF4193,这会使信道栅与 PFD 频率无关,从而大幅降低带内噪声。将 ADF4106 和 ADF4153A 进行比较(比较图 5 和图 6),可以明显看出这一优势,在 1kHz 频偏下,带内噪声从–90dBc/Hz 降至–105dBc/Hz。我们使用 ADIsimPLL™来计算,它可以对 ADI 公司的所有 PLL 产品进行了仿真。

图 4. 相位误差 QPSK。

图 5. 带 VCO-1901846T 的整数 N 分频 ADF4106。

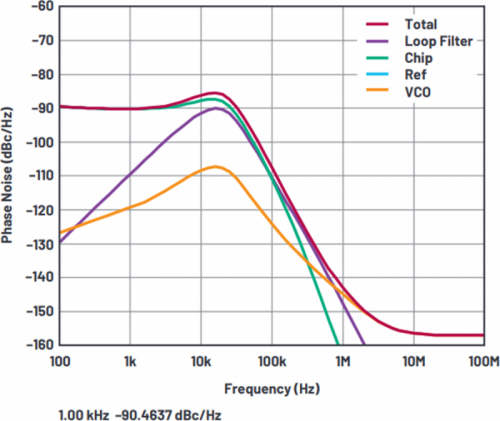

图 6. 带 VCO-1901846T 的小数 N 分频 ADF4153A。

小数 N 分频还具有额外的优势,由于 PFD 频率更高,支持的环路带宽更宽,因此锁定时间更短。利用多个电荷泵失调电流和∑-∆扰动功能,可将小数 N 杂散降低到可接受的水平。ADF4193 和 ADF4153A 分别支持 26MHz 和 32MHz PFD 频率,更高的 PFD 频率也允许用户进一步降低 N,由于整数边界杂散(IBS)的发生率和影响较小,因此可进一步改善 EVM 并简化频率规划。ADF4371 采用的最新 PLL 拓扑支持高达 160MHz 的 PFD 频率。小数 N 分频器件频率分辨率的改善(小数调制器从 12 位分辨率增加到 39 位分辨率)也意味着 PLL 可用于生成几乎所有分辨率达到毫赫(MHz),且精度极高的频率。

图 7. ADF4371。

过去,使用小数 N 分频器件遇到的主要阻碍在于存在很高的小数杂散,这些杂散由∑-∆调制器生成,会降低频谱纯度,因此需要工程师付出更多努力,以减少或消除其影响。由于 ADF4371 具有较低的小数杂散,并且没有整数边界,所以干净频谱意味着可以花费更少时间来研究、调试,或者从一定程度上消除了这些烦人的频率生成伪影带来的影响。较低的带内整数边界杂散(–55dBc)意味着一旦经 PLL 滤波器滤波,杂散就可以得到有效衰减。例如,如果将 40kHz 滤波器用于 400 kHz 信道栅,那么滤波器提供 35dB 衰减意味着距离整数边界最近信道的杂散为–90dBc。能够使用高达 160MHz 的高 PFD 频率意味着整数边界出现的几率更低,相比使用 32MHz PFD 频率,使用 160MHz PFD 频率时,其几率低 5 倍。

由于 PFD 频率和频率分辨率的提高,PLL 品质因数(FOM)也有显著提升,例如从 ADF4153 的–216dBc/Hz 提高到 ADF4371 的–233dBc/Hz(小数模式)。将图 5 和图 7 中的 ADIsimPLL 曲线进行比较,ADF4106 在整数模式下,采用 200kHz PFD 频率设置,10kHz 环路带宽,生成 1.85GHz 输出,而 ADF4371 则采用 160MHz PFD 频率设置,150kHz 环路带宽。可以看出,在 1kHz 频偏时存在 20dB 的差异,PLL 频率合成器技术取得明显进步。

同时可以看出,存在着

1ps 和 51fs 的集成 rms 相位抖动的差异。值得注意的是,与过去由电感 Q 决定 rms 噪声性能相比,带内噪声的大幅改善(通过低

FOM 和小数 N 分频实现)允许用户将环路滤波器带宽增加至 150kHz,从而抑制此带宽内的 VCO 噪声,并降低 10kHz 至

100kHz 范围内的恶化,后者一般决定 rms 噪声。为实现这一带内相位噪声的改善目标,采用更高规格的 PLL

频率参考源至关重要,通过改进此类方法的性能和灵活性,大多数用户都能接受这种权衡考量方案。在某些情况下,新型小数 N 分频 PLL

提供的更低带内噪声可以和使用偏移或转换环路的 PLL 的结果相匹敌,后者在 VCO 至 PFD

的反馈路径中使用了混频器,可大大简化要求严苛应用的频率生成。