垂直化发展的半导体封装技术将怎样的未来?

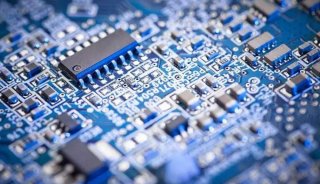

半导体封装技能的开展,使咱们平时运用的很多商品(比如手机、个人文娱设备和闪存驱动器等)的形状和功用得以完成。对那些依靠胰岛素泵和去纤颤器等可植入医疗设备的病人来说,这些3D封装技能对提高生命质量起着要害效果。不断增加的半导体商品选用笔直化开展的堆叠式裸片、层叠封装(PoP)或穿透硅通道(TSV)等封装技能,功用密度、分量和可装备性方面的优势仅仅3D封装技能广受青睐的有些缘由。每种封装办法都带来共同的优点。不过,为使这些办法充分发挥潜能,还需求采纳有针对性的设计计划、完成和剖析战略。

PoP 是增加zui敏捷的封装方法之一,TechSearch International预计,到2012这几年间,其年复合增加率将达40%。PoP所具有的可进行封装级测验以及易于选用多途径来源的才能使其变成zui受OEM期待的挑选,但这种封装技能也需审慎的协同和设计计划。典型的PoP包含基底封装内的一个大数字器材以及顶层封装内的某类存储器。存储器有也许是管脚排列固定的标准商品,所以,其封装计划没有太大灵活性。因而,设计的一个重要方面是协同顶层和底部封装的焊盘接口。当思考到存储器也许源自多个途径,而每个都也许具有不一样管脚装备时,这就将变成一个严峻的设计挑战。

多基片计划

PoP器材完成的要害是进行合理的设计计划。由于 I/O焊盘环计划和封装与封装间接口的焊盘直接相关,所以PoP计划应优先或一起于芯片层的计划。抱负状况是,接口变成设计计划的起点;存储器器材规则焊盘安置,并且必要时,I/O焊盘环方位要进行修正。在进行计划时,要将裸片张贴办法思考在内,由于用于线绑定的指状焊片装备以及用于倒装芯片的凸点方法,在封装接口焊盘和I/O焊盘环间起到中介衔接点的效果。其它的计划思考要素包含,底层封装的可布线性、网络名区别以及主印制板(PCB)。方针是完成一个满意内核逻辑衔接性需求的I/O焊盘环计划,能取得zui具本钱效益的封装计划,例如,层数和过孔数起码,走线zui短。

这种贯穿芯片、多种封装,甚至在某些场合还包含PCB的协同化设计计划给传统办法学带来严峻挑战,尤其是对选用不一样东西和数据库进行封装和芯片设计的次序设计流程。因而,设计团队常常需求协作,运用电子表格交流焊盘装备设计。但这种办法的缺陷在于,它是根据静态数据的“快照”,会致使大量迭代、易于犯错的流程,这对缩短设计周期、降低本钱起不到多大效果。

新一代EDA东西(例如Sigrity公司的OrbitIO Planner),经过将悉数数据资源整合进一个公共的、一体化的计划环境中,给并行设计计划及其可行性带来立异办法。在设计还处在计划期间时,线绑定和布线可行性功用就可供给多种办法,去评价与详细设计完成相关的各个方面。这种办法使焊盘安置变得简单,并且能在全部体系环境中揣度并评价各种衔接状况。一个一体化的芯片-封装-PCB数据模型主动将设计元素的改动衍播至附近区域,对体系范围内的影响供给瞬时反应。在详细设计完成之前,优化I/O焊盘环和封装到封装的衔接性,以改善功用、本钱和可制作性,然后终究取得及时、有用的PoP开发成果。

前瞻性建模

在设计流程的前期运用抽取成果,可使设计人员可以了解拓扑构造和完成挑选对体系级行动发生的影响。在了解信号负载、延时、反射和耦合等状况以后,I/O设计人员可完成更加牢靠的片上驱动器。类似地,在设计前期运用封装电源面和片上电源栅格电气模型,可使设计人员对封装和芯片之间的去耦电容安置进行权衡,以完成具有功用、zui低本钱的设计。

运用可行性研究生成的迹线和线绑定长度,设计人员可大致估计信号网络的寄生参数。不过,获取功率传输体系寄生参数需求某种方法(即便近似)的物理完成。不连续的回来途径、电源面的共振以及去耦战略取决于物理完成。因而,在思考是不是切割功率传输面以及它们与信号完好性的交互效果方面,完好的封装获取为做出终究挑选供给了很好的支撑。这种挑选有必要在封装设计流程的前期就断定下来;在设计流程后期很难改动,即便获取量仅被用于终究验证,或为同事或客户供给终究设计的电气模型。

TSV封装是一种笔直封装方法,它有望完成更高的集成密度并支撑高带宽的存储-逻辑接口。一些观点以为,当仅凭半导体技能自身无法完成芯片缩放时,TSV封装可作为完成这一方针的手法。

在 TSV技能中,是运用硅片上的通孔将裸片堆叠并直接相连,而不是选用线绑定或凸点焊接。虽然技能技能不断演进,一些办法是先做过孔,而另一些是后做过孔,但都需求高度的协同设计计划,以便在思考部分片上互连的一起,和谐基底间的过孔方位。不过,要害的问题是缺少TSV计划和完成东西,而这会影响该技能取得广泛选用。

堆叠式裸片封装是另一种笔直封装方法,它将若干裸片以堆叠方法集成进单个封装中。与传统封装器材比较,这种方法的高度硅集成极大减小了所需的PCB面积。裸片间的严密堆叠使该方法变成完本钱地化高速、高带宽互连的抱负挑选,进一步降低了对PCB的请求。与PoP技能比较,堆叠式裸片封装能以更小的体积和分量供给更高的功用密度,但对牢靠性和测验的请求有必要贯穿在全部设计思考中。

在开发过程中,堆叠式裸片封装的设计计划至关重要,这极大地影响到终究商品的复杂性和本钱。

-

焦点事件

-

精英视角