半导体的3D时代(二)

图3在左轴上显示了按年份和公司分类的串堆叠,在右轴上显示了每个单元的最大比特数。

图3.堆叠层数,每单元比特数。

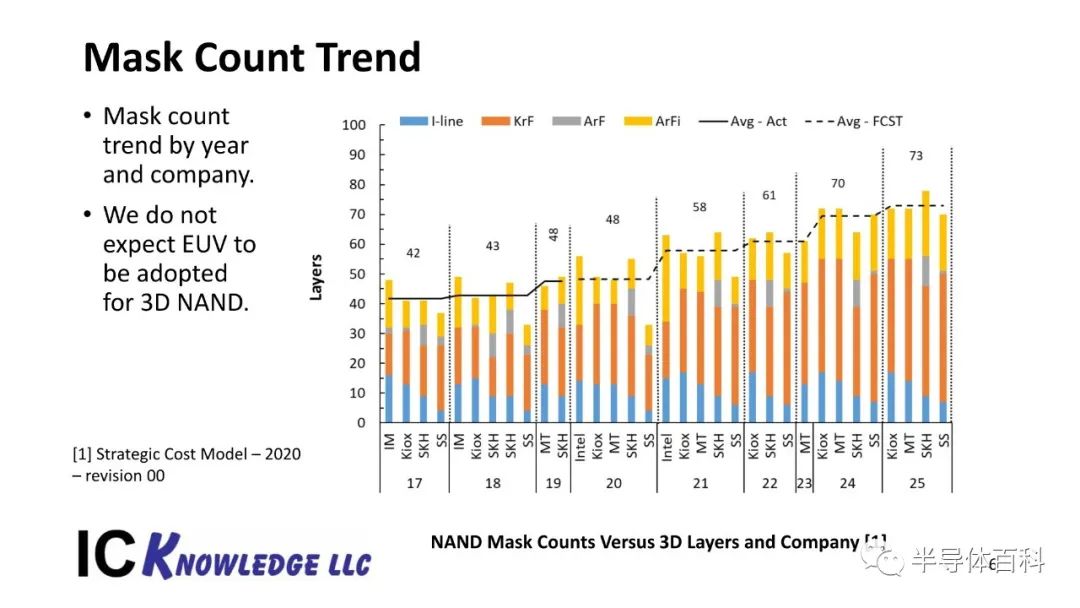

图4展示了我们对按曝光类型,公司和年份划分的掩模数量的分析。虚线是每年的平均掩模数,从2017年的42张增加到2025年的73张,这与层数从2017年的平均60个增加到2025年的512个相对应。换句话说,掩模数量仅增加1.7倍就增加了8.5倍的层数以突出3D NAND工艺的掩模使用效率。

图4.掩模数量趋势。

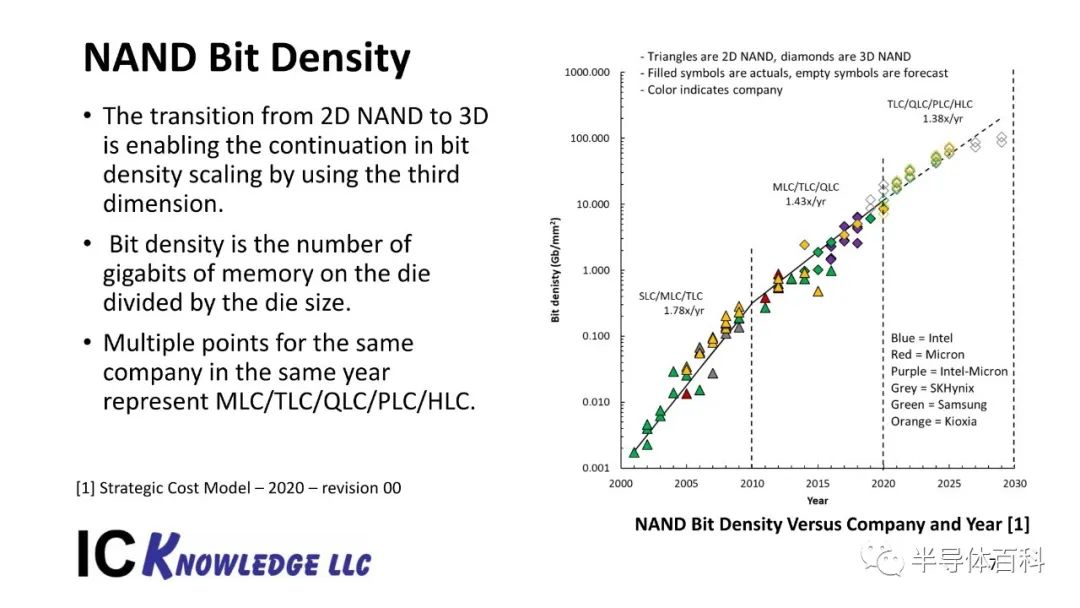

图5展示了各家公司2D NAND和3D NAND的实际和预测比特密度随年份变化的趋势。这里是整个芯片的比特密度,即芯片的容量除以芯片的尺寸。

图5. NAND比特密度。

从2000年到2010年,在光刻微缩的推动下,2D NAND比特密度每年增长1.78倍。大约在2010年左右,继续缩小2D NAND的难度导致增长减慢至1.43倍,直到2015年左右3D NAND成为驱动力并继续以每年1.43倍的速度增长。我们预计从2020年到2025年的年增长率将略有下降,为1.38倍。与去年相比,这是我们的预测的一项改进,因为我们看到这些公司推动该技术的速度超出了我们最初的预期。最后,SK海力士谈到了2025年的500层和2030年的800层,导致2025年之后的速度进一步放缓。

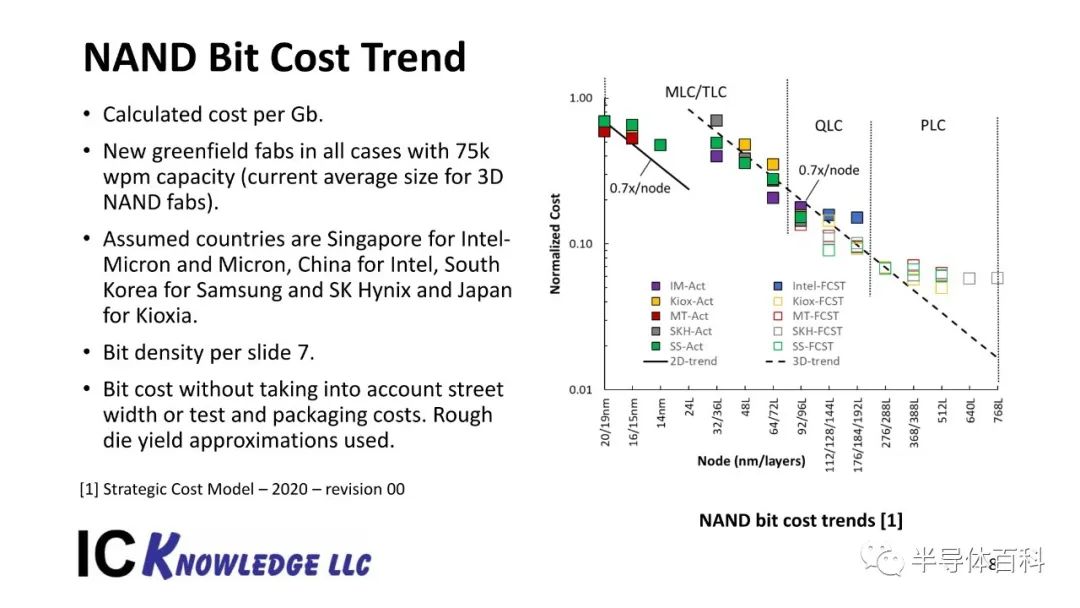

图6给出了NAND单位比特成本趋势。

图6. NAND单位比特成本。

在该图中,我们采用了使用战略成本和价格模型计算出的晶圆成本,并将其与图5中的位密度相结合以产生单位比特成本趋势。在所有情况下,这些晶圆厂都是新建的月产能75,000片晶圆的工厂,因为这是NAND晶圆厂在2020年的平均产能。这些晶圆厂对应所在的国家分别是新加坡-英特尔美光,英特尔-中国,Kioxia-日本,三星和SK海力士-韩国。这些计算不包括封装和测试成本,不考虑划片槽宽度,并且仅包含粗略的芯片良率假设。

图表中的前三个节点是2D NAND,每个节点的成本趋势为0.7倍。随着向3D NAND的过渡,大多数公司的比特成本最初都增加了,但现在已降至2D NAND比特成本以下,并且每个节点的趋势为0.7倍,直到大约300到400层。我们预计单位比特成本会趋于平缓,除非在工艺或设备效率方面取得一些突破,否则该技术将面临成本极限。

-

焦点事件

-

精英视角