后FinFET时代的技术演进(二)

需要微缩助推器

在6T和5T的低单元高度下,向Nanosheet器件的迁移变得最佳,因为在这种情况下,fin的减少会降低传统基于FinFET的单元中的驱动电流。

但是,如果不引入结构化微缩助推器(如埋入式电源轨和环绕式接触),就无法将单元高度从6T减小到5T。

电源轨为芯片的不同组件提供电源,并且一般由BEOL中Mint和M1层提供。但是,它们在那里占据了很大的空间。在嵌入式电源轨结构中,电源轨埋在芯片的前段,以帮助释放互连的布线资源。此外,它们为采用节距微缩而增加BEOL电阻的技术提供了较低的电阻局部电流分布。BEOL没有电源轨后,可以将标准单元的高度从6T进一步降低到5T。

下一步:缩小p和n之间的间距

随着走向更小的轨道高度的旅程的继续,单元高度的进一步减小将要求标准单元内nFET和pFET器件之间的间距更小。但是,对于FinFET和Nanosheet而言,工艺限制了这些n和p器件之间的间距。例如,在FinFET架构中,通常在n和p之间需要2个dummy fin的间距,这最多消耗总可用空间的40-50%。

为了扩大这些器件的可微缩性,IMEC最近提出了一种创新的架构,称为Forksheet器件。Forksheet可以被认为是Nanosheet的自然延伸。

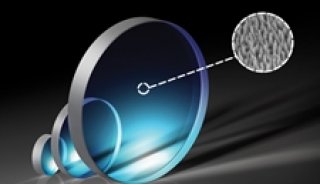

与Nanosheet相比,现在沟道由叉形栅极结构控制,这是通过在栅极图案化之前在p和nMOS器件之间引入“介电墙”来实现的。该墙将p栅沟槽与n栅沟槽物理隔离,从而允许更紧密的n到p间距。

从FinFET到Nanosheet再到Forksheet的自然演变。

用于制造Forksheet的工艺流程与用于制造Nanosheet的工艺流程相似,仅增加一些额外的工艺步骤。n和p之间的介电隔离还具有一些工艺优势,例如填充功函数金属的工艺更简化。在此基础上,由于大幅减少了n到p的间距,预计该Forksheet具有更佳的面积和性能的可微缩性。

Forksheet工艺流程中的关键步骤,即有源区形成后“介电墙”的形成步骤。