如何利用CMR机制优化电路板设计及布局(二)

接近角度

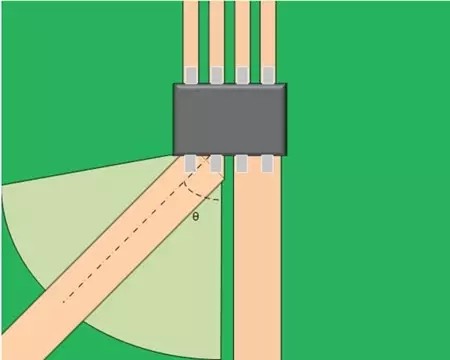

使用Allegro电流传感器IC的一个常见错误是使用不适当的电流引入角度。图6是电流轨迹接近IC的示例(此处是ACS724)。此图显示IP+和IP–的轨迹。浅绿色区是进入IP+的理想接近区。该区域范围是0°至85°。该规则同样适用于IP–轨迹。

该区域的限制是为了防止载流轨迹影响到可能导致IC输出误差的任何杂散场。如果与IP相连的电流轨迹在该区域外部,则必须按上述方式处理(临近电流路径导致的磁场)。

图6:ACS724电流轨迹接近角度θ的理想范围是0°至85°,此范围很可能与其他Allegro电流传感器IC不同。

IC下的扩展

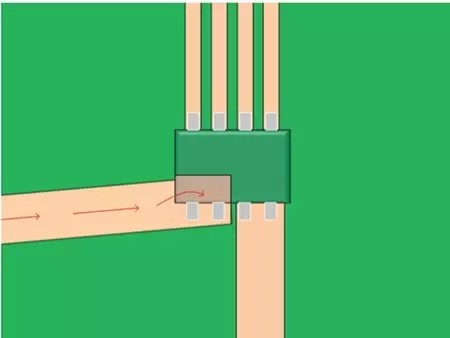

另一个常见错误是电流轨迹与IP管脚距离过远。根据器件的不同,这可能导致两种不同的问题。如果是采用SOIC和类似封装的器件,这可能导致IC上产生杂散场,使性能降低。如果采用LR封装,由于IP总线较大并且暴露在外,在封装下面过远布线可能改变通过IP总线的电流路径,从而改变器件的性能。下面内容将更详细地介绍对LR封装的影响。

对于杂散场而言,如果电流轨迹以一定的角度进入IP总线,问题会更加严重。如果发生这种情况,电流实际在部件下面流过,背向IP管脚,然后向上通过IP管脚。改变的电流路径可能会导致杂散场产生,降低IC精度。禁止在器件下面扩展至IP管脚的电流轨迹就可以防止这种情况。

图7:ACS724在IC下扩展,电流轨迹在IC下面过远,改变了电流路径,降低了精度。

永磁体影响

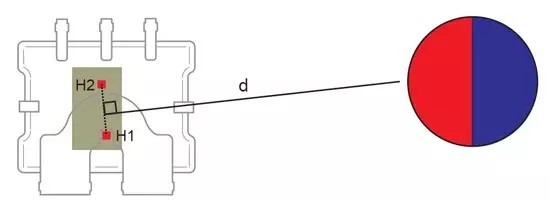

如果永久磁铁靠近电流传感器IC,磁铁导致的杂散场也会影响IC性能。一般情况下,来自磁铁的杂散场可能随磁体的不同而变化极大。它取决于磁铁尺寸、材料、磁化方向以及其他很多因素。如果可以调整电流传感器,使霍尔板垂直于磁体(如图8所示),则可以将这些杂散场的影响降至最小。

图8:具有临近永磁体最优方向的ACS780。

LR封装特定布局规则

IC下的扩展

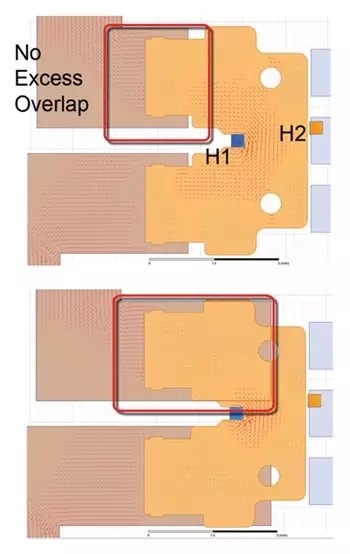

在LR封装中,载流轨迹在器件下面扩展实际改变了电流通过IP总线的路径。这可能导致IP总线与IC的耦合因数发生变化,并显著降低器件性能。

使用ANSYS Maxwell电磁套件可以模拟电流密度和电流产生的磁场。图9提供两种不同模拟的结果。第一种情况是向上引至IP总线的电流轨迹在所需点终止。第二情况是电流轨迹向IP总线上方扩展过远。两个模拟中的红色箭头表示高电流密度的区域。在没有过量重叠的模拟中(红色区域),电流密度与具有过量重叠的模拟差距巨大。还可以看出,H1场比没有过多重叠时更大。这一点用蓝色暗影表示。

图9:具有不同电流轨迹和IP总线重叠的ACS780引线框模拟。

如果重叠超过推荐量,也会导致其他问题,例如电流接近角范围显著缩小。如果电流轨迹在IP总线上扩展的过大,则会形成对接近角的依赖,即接近角直接影响器件的耦合因数。避免这种情况的最佳方式是限制电流轨迹的重叠。

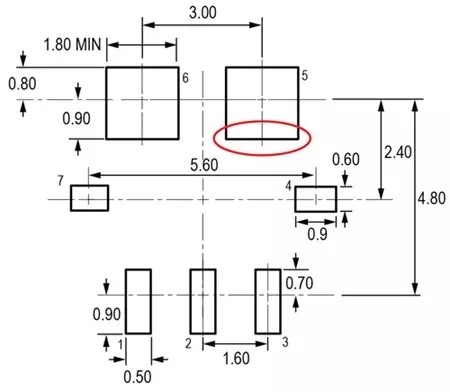

图10:ACS780 PCB布局参考图。进行必要的调整,满足应用工艺要求和PCB布局公差和红色的圈选关键尺寸。

结论

Allegro MicroSystems电流传感器IC有很多优势。这些传感器IC的磁滞几乎为零,而且功耗非常低。与无磁芯相伴的一个缺点是容易受到杂散磁场的影响。但是,很多IC都能够抑制共模磁场。

两个霍尔板的共模场相等时,CMR技术效果最好。我们探讨了若干显著降低两个霍尔板共模场差值的技术,即如何进行外部电流路径布线与其他优化布局技术。针对电流路径不能以最有利的方向布线的情况,我们还介绍了误差估算。此外,还探讨了一些针对LR封装的布局技术,这是因为必须考虑LR的一些特性才能获得最优性能。