深度解读:到底什么是IGBT?(二)

1)高电压:一般的MOSFET如果Drain的高电压,很容易导致器件击穿,而一般击穿通道就是器件的另外三端(S/G/B),所以要解决高压问题必须堵死这三端。Gate端只能靠场氧垫在Gate下面隔离与漏的距离(Field-Plate),而Bulk端的PN结击穿只能靠降低PN结两边的浓度,而最讨厌的是到Source端,它则需要一个长长的漂移区来作为漏极串联电阻分压,使得电压都降在漂移区上就可以了。

2) 大电流:一般的MOSFET的沟道长度有Poly CD决定,而功率MOSFET的沟道是靠两次扩散的结深差来控制,所以只要process稳定就可以做的很小,而且不受光刻精度的限制。而器件的电流取决于W/L,所以如果要获得大电流,只需要提高W就可以了。

所以上面的Power MOSFET也叫作LDMOS (Lateral Double diffusion MOS)。虽然这样的器件能够实现大功率要求,可是它依然有它固有的缺点,由于它的源、栅、漏三端都在表面,所以漏极与源极需要拉的很长,太浪费芯片面积。而且由于器件在表面则器件与器件之间如果要并联则复杂性增加而且需要隔离。所以后来发展了VDMOS(Vertical DMOS),把漏极统一放到Wafer背面去了,这样漏极和源极的漂移区长度完全可以通过背面减薄来控制,而且这样的结构更利于管子之间的并联结构实现大功率化。但是在BCD的工艺中还是的利用LDMOS结构,为了与CMOS兼容。

再给大家讲一下VDMOS的发展及演变吧,最早的VDMOS就是直接把LDMOS的Drain放到了背面通过背面减薄、Implant、金属蒸发制作出来的(如下图),他就是传说中的Planar VDMOS,它和传统的LDMOS比挑战在于背面工艺。但是它的好处是正面的工艺与传统CMOS工艺兼容,所以它还是有生命力的。但是这种结构的缺点在于它沟道是横在表面的,面积利用率还是不够高。

再后来为了克服Planar DMOS带来的缺点,所以发展了VMOS和UMOS结构。他们的做法是在Wafer表面挖一个槽,把管子的沟道从原来的Planar变成了沿着槽壁的

vertical,果然是个聪明的想法。但是一个馅饼总是会搭配一个陷阱(IC制造总是在不断trade-off),这样的结构天生的缺点是槽太深容易电场集中而导致击穿,而且工艺难度和成本都很高,且槽的底部必须绝对rouding,否则很容易击穿或者产生应力的晶格缺陷。但是它的优点是晶饱数量比原来多很多,所以可以实现更多的晶体管并联,比较适合低电压大电流的application。

还有一个经典的东西叫做CoolMOS,大家自己google学习吧。他应该算是Power MOS撑电压最高的了,可以到1000V。

3、IGBT的结构和原理

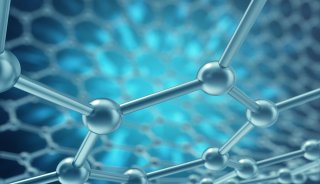

上面介绍了Power MOSFET,而IGBT其实本质上还是一个场效应晶体管,从结构上看和Power

MOSFET非常接近,就在背面的漏电极增加了一个P+层,我们称之为Injection Layer (名字的由来等下说).。在上面介绍的Power MOSFET其实根本上来讲它还是传统的MOSFET,它依然是单一载流子(多子)导电,所以我们还没有发挥出它的极致性能。所以后来发展出一个新的结构,我们如何能够在Power MOSFET导通的时候除了MOSFET自己的电子我还能从漏端注入空穴不就可以了吗?所以自然的就在漏端引入了一个P+的injection layer(这就是名字的由来),而从结构上漏端就多了一个P+/N-drift的PN结,不过他是正偏的,所以它不影响导通反而增加了空穴注入效应,所以它的特性就类似BJT了有两种载流子参与导电。所以原来的source就变成了Emitter,而Drain就变成了Collector了。

从上面结构以及右边的等效电路图看出,它有两个等效的BJT背靠背链接起来的,它其实就是PNPN的Thyristor(晶闸管),这个东西不是我们刻意做的,而是结构生成的。我在5个月前有篇文章讲Latch-up(http://ic-garden.cn/?p=511)就说了,这样的结构最要命的东西就是栓锁(Latch-up)。而控制Latch-up的关键就在于控制Rs,只要满足α1+α2<1就可以了。

-

人物动向

-

焦点事件

-

焦点事件

-

焦点事件

-

综述

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件