逻辑分析仪基础知识(三)

状态分析

状态分析仪需要来自被测设备的采样时钟信号。这种类型的时钟计时可使逻辑分析仪中的数据采样与被测设备中的计时事件同步。具体来讲:

状态分析仪适用于显示“有效时钟或控制信号”期间的信号活动是“什么”。

状态分析仪侧重于查看指定执行时间内的信号活动,而不是与时序无关的信号活动。

这就是为什么状态分析仪需要对与被测设备时钟信号“同步化”或同步的数据进行采样。

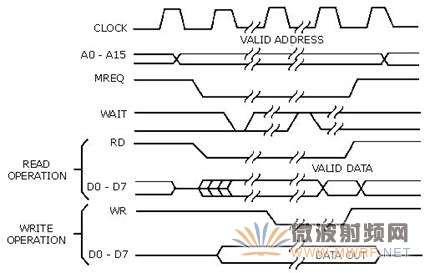

对于微处理器,数据和地址可以出现在相同的信号线上。要采集正确的数据,逻辑分析仪必须对数据采样加以限制,使之只在所需的数据有效并出现在信号线上时进行。为此,它会从相同的信号线上采集数据样本,但使用来自被测设备的不同采样时钟。

示例:以下时序图表明,要采集地址,分析仪需要在 MREQ 线下降时进行采样。

要采集数据,分析仪需要在 WR 线下降(写周期)或 RD 线下降(读周期)时进行采样。

图7 状态采集

触发状态分析仪:

与定时分析仪相似,状态分析仪也具有限定要存储的数据的功能。如果我们正在查找地址总线的上限和下限的特定码型,当分析仪找到该码型时,我们可以通知分析仪开始存储,并且只要分析仪的内存未满就一直存储。

简单触发示例:

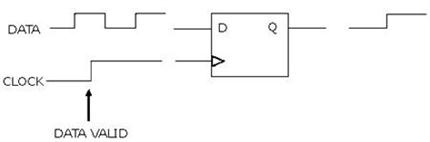

请看下面显示的“D”触发器,在正值的时钟沿出现之前,“D”输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。

图8 D触发器

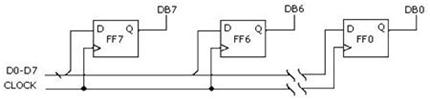

现在,假设我们有并行的八个此类触发器。如下所示,这八个触发器都连接到同一时钟信号。

图9 接收器

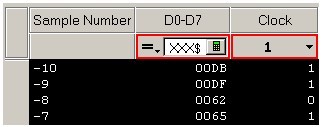

当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在 D0 - D7 这几条上收集数据。

图10 总线收集的数据

高级触发示例:

假设想查看地址值为 406F6 时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型 406F6(十六进制)以及在 RD(内存读取)时钟线上查找高电平。

图11 高级触发设置

在配置 Edge And Pattern trigger(时钟沿和码型触发)对话框时,尝试将该操作看作是构造从左向右读取的句子。

Find the first occurrence of a Bus named ADDR, and on All bits a pattern that Equals 406F6 Hex, And a Signal named RD with a High level.Then Trigger and fill memory with Anything.

-

焦点事件

-

政策法规

-

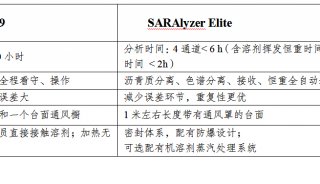

产品技术

-

焦点事件

-

企业风采

-

焦点事件

-

会议会展

-

招标采购

-

企业风采

-

企业风采

-

焦点事件

-

企业风采

-

产品技术

-

会议会展

-

招标采购

-

焦点事件

-

综述

-

焦点事件

-

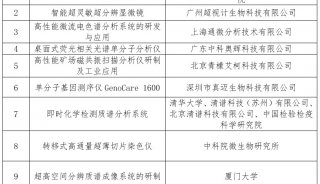

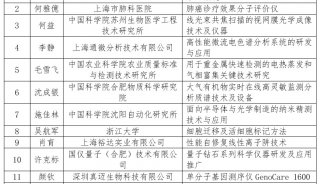

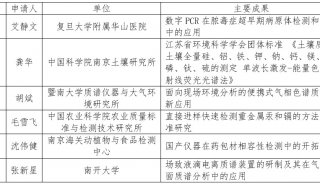

项目成果

-

科技前沿

-

科技前沿

-

企业风采

-

焦点事件

-

焦点事件

-

焦点事件

-

项目成果

-

焦点事件

-

焦点事件

-

产品技术

-

会议会展