台积电5nm SRAM技术细节解析(三)

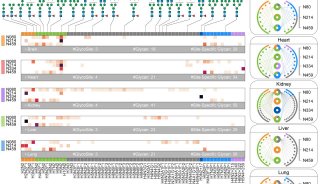

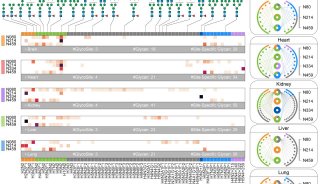

图8显示了具有不同位线配置的NBL耦合电平,表明可配置金属电容器C1可以随位线长度调节,从而可以减轻具有不同位线长度的耦合NBL电平的变化。

图8.具有不同位线配置的NBL耦合电平。

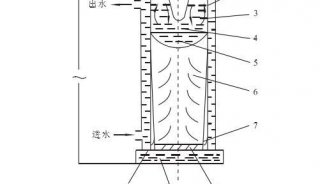

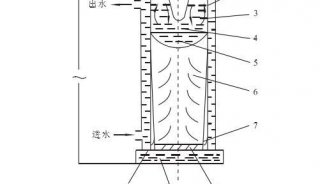

写入辅助的第二种方法是降低单元VDD(LCV)。LCV的常规技术需要强偏置或有源分压器才能在写操作期间调整列式存储单元的电源电压,但是这些技术在整个工作时间内会消耗大量的有功功率。脉冲下拉(PP,Pluse Pull-down)和电荷共享(CS,Charge Sharing)技术是两种替代解决方案,但PP难以精确计时。因此,如图9所示,台积电提出了使用阵列顶部的金属线作为电荷共享电容器来实现CS方案。

图9.使用SRAM阵列顶部的CS金属走线实现LCV的电荷共享,以实现写辅助。

推荐

-

招标采购

-

招标采购

-

企业风采

-

招标采购

-

企业风采

-

企业风采

-

焦点事件

-

项目成果

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

招标采购

-

焦点事件

-

项目成果

-

焦点事件

-

科技前沿

-

企业风采

-

技术原理

-

焦点事件

-

焦点事件

-

企业风采

-

焦点事件

-

焦点事件

-

科技前沿

-

技术原理

-

焦点事件

-

焦点事件

-

焦点事件