围殴DDR系列之设计与仿真分析篇

作为高速先生的宝藏话题,DDR的设计与仿真一直是我们关注的重点,上周五的文章介绍了DDR的发展历史、关键技术和JEDEC标准,本周继续对DDR设计及仿真分析的文章进行分类导读。

01

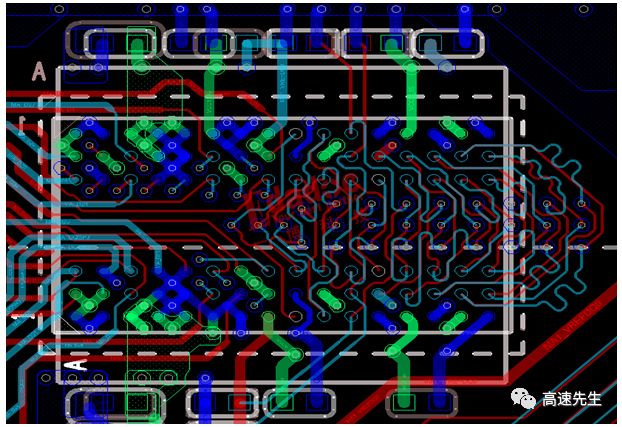

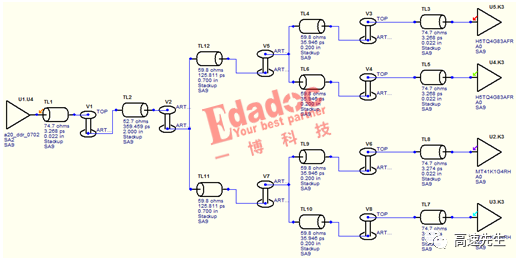

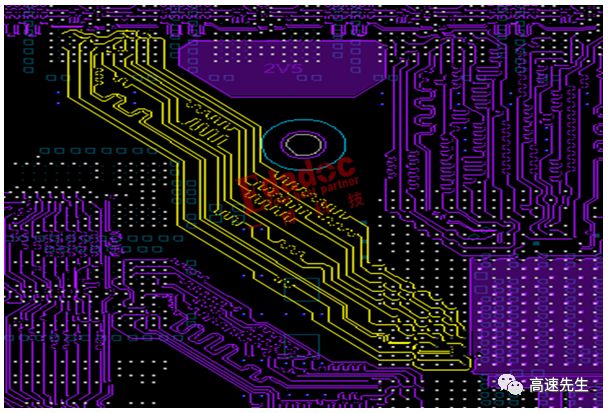

对于Layout工程师而言,最关心的莫过于DDR的设计要点。比如,在布局阶段,需要评估DDR走线拓扑对布局的影响(主要针对地址控制类信号)、滤波电容的布局要求、VREF电路布局、匹配电阻的布局等;在布线阶段,除了走线拓扑,还需要关注等长要求和电源设计。《DDR3布局的那些事儿》、《DDR3布线的那些事儿》

02

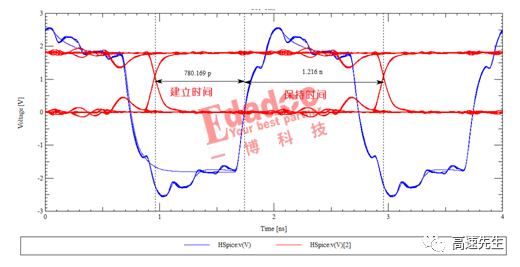

提到DDR设计,少不了线长匹配和时序要求,对于DDR等长要求的总体原则是:地址、控制/命令信号与时钟做等长。DQ/DM信号与DQS做等长。本文用仿真实例向大家展示DDR中地址相对于时钟的建立时间与保持时间。《DDR线长匹配与时序(上)》

03

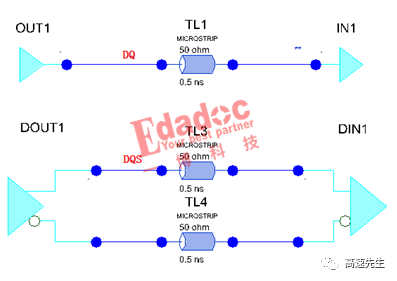

数据信号与DQS又是什么样的关系呢?DDR和普通的SDRAM相比,读取速率翻番,这个又该怎么理解?对等长要求的影响如何?《DDR线长匹配与时序(下)》

04

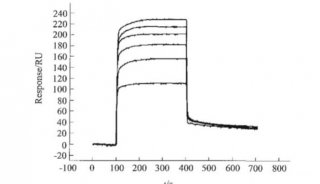

DDR信号网络多,走线密度大,速率较高,DDR信号质量直接关系到整块板子的设计成败,此时,仿真分析会为我们的设计提供有力的支撑。本文通过几个案例让初学者对DDR仿真有一个简单的认识。《DDR信号完整性仿真介绍一》、《DDR信号完整性仿真介绍二》

05

此外,对于DDR这种并行信号的串扰该如何评估?希望这篇文章对你有所启发。《几张图让你轻松理解DDR的串扰》

-

综述

-

项目成果

-

企业风采

-

精英视角

-

精英视角

-

精英视角

-

精英视角

-

精英视角

-

项目成果

-

焦点事件

-

会议会展

-

市场商机

-

企业风采

-

会议会展

-

焦点事件

-

焦点事件

-

科技前沿

-

焦点事件

-

企业风采

-

会议会展

-

科技前沿

-

精英视角

-

焦点事件

-

企业风采

-

焦点事件

-

企业风采

-

焦点事件

-

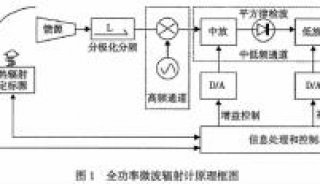

技术原理

-

企业风采

-

产品技术

-

焦点事件

-

焦点事件

-

实验室动态

-

会议会展

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

焦点事件

-

科技前沿

-

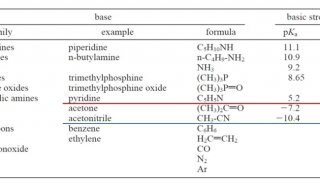

科技前沿