数字下变频器的发展和更新(二)

推荐

-

焦点事件

-

焦点事件

-

政策法规

-

焦点事件

-

焦点事件

-

企业风采

-

焦点事件

-

精英视角

-

政策法规

-

科技前沿

-

精英视角

-

企业风采

-

焦点事件

-

焦点事件

-

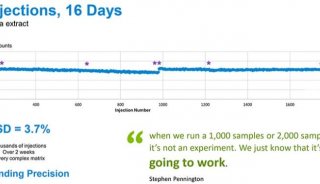

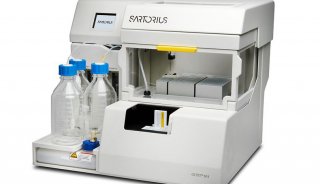

产品技术

-

综述

-

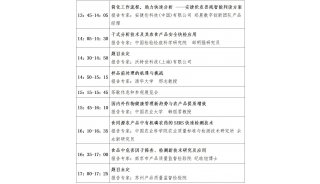

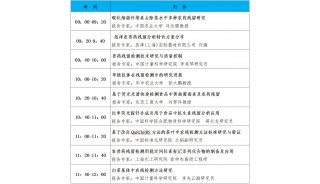

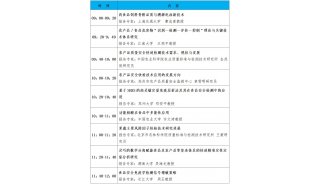

会议会展

-

焦点事件

-

会议会展

-

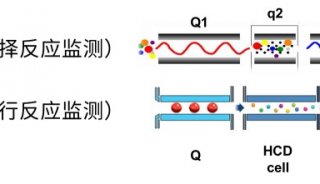

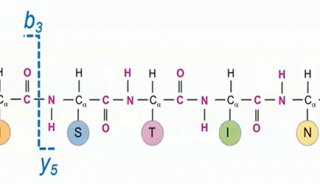

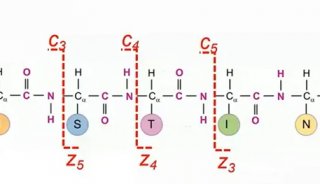

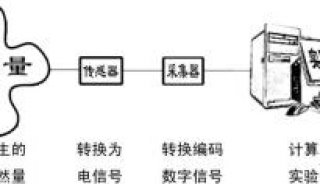

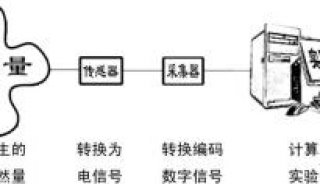

技术原理

-

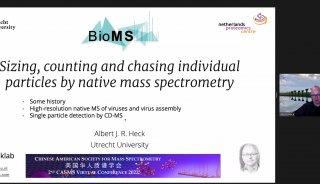

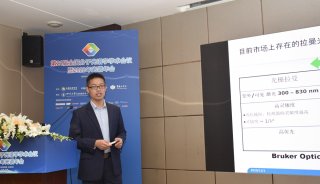

会议会展

-

会议会展

-

焦点事件

-

焦点事件

-

焦点事件

-

会议会展

-

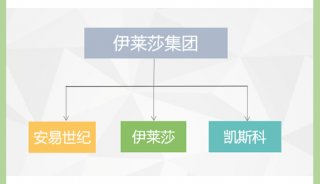

企业风采

-

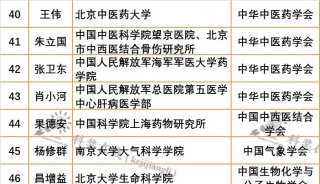

精英视角

-

焦点事件

-

精英视角

-

焦点事件

-

技术原理

-

项目成果

-

技术原理

-

焦点事件

-

焦点事件

-

技术原理